# A physics-based electro-thermal model for FS IGBT

<sup>1</sup>The School of Reliability and System Engineering, Beihang University, Beijing 100191, China.

<sup>2</sup>The School of Reliability and System Engineering, Beihang University, Beijing 100191, China.

<sup>a</sup>chengyu732@buaa.edu.cn, <sup>b</sup>fuguicui@buaa.edu.cn

**Keywords:** FS IGBT, electro-thermal model, Fourier-based, RC network

**Abstract.** A physics-based electro-thermal model implemented in the Matlab/Simulink is introduced for FS (field stop) IGBT (Insulated Gate Bipolar Transistor) in this paper. The model consists of Fourier-based FS IGBT model and equivalent RC thermal network model. The static testing of a commercial IGBT is performed to validate the model. The comparison between the simulation and experiment results proves the accuracy and efficiency of the model.

## Introduction

Nowadays, the FS IGBT (Insulated Gate Bipolar Transistor) is playing an important role in modern power converter systems and current applications [1]. There is in great need in characterize the FS IGBT account accurately. The thermal compact model is equally important as its electrical counterpart and should be included in the compact model. Review all the FS IGBT model available [2]-[5], only very few models presented take the self-heat effect into consideration. So it is necessary to develop an accurate compact model for this new generation power device.

In this paper, a physics-based electro-thermal (ET) model for FS IGBT is proposed. The Fourier-based compact model is to characterize the FS IGBT while the self-heat effect is described by an equivalent RC network model. Finally, the static experiment of FS IGBT under resistive-load circuit is performed to validate the model, and the simulation results of forward conduction characteristics shows a great accordance in the experiment.

## Fourier-based solution FS IGBT model

The proposed FS IGBT model is based on a model developed for NPT IGBT and described in [6], [7]. In the model, the high-level injection and quasi-neutral are assumed, and the dynamics of excess carrier in N-base is governed by ADE

$$D\frac{\partial^2 p(x,t)}{\partial x^2} = \frac{p(x,t)}{\tau} + \frac{\partial p(x,t)}{\partial t}$$

(1)

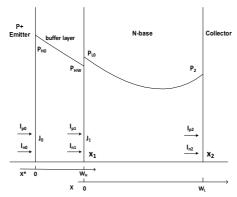

where  $D = 2D_nD_p/(D_n + D_p)$  is the ambipolar diffusion coefficient,  $D_p$  and  $D_n$  are the hole and electron diffusion coefficients, respectively.  $\tau$  is the high-level excess carrier lifetime. p(x,t) is the excess carrier concentration. Fig. 1 defines some of the relevant variables used in this Fourier-based solution model. The boundary conditions needed to solve the ADE are the gradients of the carrier concentration at  $x_1$  and  $x_2$ , which are given by

$$\left. \frac{\partial p}{\partial x} \right|_{x_1} = \frac{1}{2qA} \left( \frac{I_{n1}}{D_n} - \frac{I_{p1}}{D_p} \right) \tag{2}$$

$$\left. \frac{\partial p}{\partial x} \right|_{x_2} = \frac{1}{2qA} \left( \frac{I_{n2}}{D_n} - \frac{I_{p2}}{D_p} \right) \tag{3}$$

where A is the device area.  $I_{n1}$  and  $I_{p1}$  are electron and hole current at  $x_1$ .  $I_{n2}$  and  $I_{p2}$  are electron and hole current at  $x_2$ .

The current continuity requires

$$I_C = I_{n1} + I_{p1} = I_{n2} + I_{p2} (4)$$

Fig. 1 Boundary condition definition for FS IGBT

Assuming buffer layer is in high-level injection condition [7], the hole concentration  $P_{HW}$  at the boundary between the buffer layer and the N-base is given by

$$P_{HW}(P_{HW} + N_H) = P_{L0}(P_{L0} + N_B) = P_{L0}^2 \tag{5}$$

where  $N_H$  is the doping concentration of the LPT n buffer layer. The hole current  $I_{p0}$  at the  $J_0$  junction can be easily obtained by

$$I_{p0} = \frac{qAD_{pH}}{L_{pH}\sinh\left(\frac{W_H}{L_{pH}}\right)} \left[P_{H0}\cosh\left(\frac{W_H}{L_{pH}}\right) - P_{HW}\right] + \frac{I_C}{1 + b_L}$$

$$(6)$$

The hole current  $I_{p1}$  at the  $J_1$  junction can be similarly obtained as

$$I_{p1} = \frac{qAD_{pH}}{L_{pH}\sinh\left(\frac{W_H}{L_{pH}}\right)} \left[P_{H0} - P_{HW}\cosh\left(\frac{W_H}{L_{pH}}\right)\right] + I_{QH} + \frac{I_C}{1 + b_L}$$

$$(7)$$

The voltage across junction  $J_0$  is

$$V_{J0} = V_T \ln \left( \frac{P_{H0} N_H}{n_i^2} \right) \tag{8}$$

and the voltage across junction  $J_1$  is

$$V_{J1} = V_T \ln \left( \frac{N_B}{P_{L0}} \right) \tag{9}$$

These equations are used with the NPT IGBT model proposed in [6], [7] to modeling FS IGBT.

# Equivalent RC network thermal model

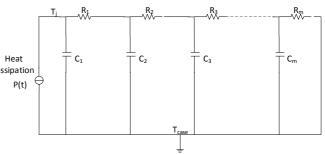

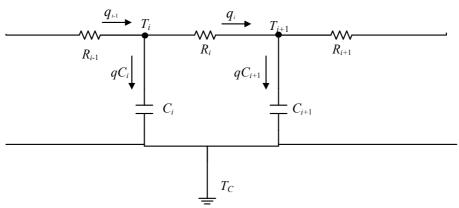

The equivalent RC network thermal model [8] is based on the thermal property of different packaging materials. The schematic of this equivalent RC network is shown in Fig. 2. In order to obtain the thermal resistance and capacitance directly from the geometry of package, the equivalent RC network need to be changed to the network shown in Fig. 3.

Fig. 2 The Foster equivalent RC thermal network

Fig. 3 The Cauer equivalent RC thermal network

The resistances are a lumped representation of the distributed thermal resistance network of the component, from die to ambient, while the capacitances are a lumped representation of distribution of heat capacitance. Each group of resistor and capacitor represents different layers of thermal spreading path, which is from heat source to the heat sink or base plate. The heat sink could also be considered simply to add another two RC components for the heat transfer from case to heat sink and from heat sink to ambient respectively. The thermal resistance and capacitance are obtained from:

$$R_i = \frac{d_i}{k_i A_i} \tag{10}$$

$$C_i = c_i \rho_i V_i \tag{11}$$

where  $d_i$  is the depth,  $A_i$  is effective cross-section area,  $V_i$  is effective volume.  $k_i$  is thermal conductivity. The two coefficients, thermal conductivity,  $k_i$ , and the specific heat capacity,  $c_i$ , are temperature dependent. The results for the different layers of the package are presented in Table. 1 [9].

Table. 1 Conductivity and specific heat capacity of the different layers

(From References [9])

| (FIGHT References [9]) |                            |          |                                      |          |           |  |

|------------------------|----------------------------|----------|--------------------------------------|----------|-----------|--|

|                        | Thermal Conductivity $k_i$ |          | Specific Heat Capacity $c_i$         |          |           |  |

| Material               | Power Fit: $k_i = aT^b$    |          | Quadratic Fit: $c_i = a + bT + dT^2$ |          |           |  |

|                        | а                          | b        | а                                    | b        | d         |  |

| Copper                 | 608.0409                   | -0.07305 | 1.78E+02                             | 2.36E+00 | -2.06E-3  |  |

| Silicon                | 438056.1                   | -1.40022 | 2.93E+02                             | 3.96E-01 | -3.20E-04 |  |

| AIN                    | 1.31E+08                   | -2.2626  | 819.7                                | 0        | 0         |  |

| solder                 | 241.8863                   | -0.22605 | 134                                  | 0        | 0         |  |

Fig. 4 A part of RC thermal circuit diagram

A part of a RC circuit is presented in Fig. 4. Kirchoff's current law is used to describe the circuit. For the node *i*, the equation is:

$$qc_{i-1} = q_{i-1} - q_i (12)$$

The heat flow,  $q_i$ , through the thermal resistor,  $R_i$ , is calculated using Ohm's law:

$$q_{i} = \frac{T_{i} - T_{i+1}}{R_{i}} \tag{13}$$

The temperature difference across the two nodes of the capacitor  $C_i$  is calculated by:

$$T_i - T_C = \frac{1}{C_i} \int qc_i dt \tag{14}$$

The input current source of equivalent RC network is the heat dissipation generated from semiconductor chip. This is the connecting joint between thermal model and electrical simulation model. The dissipated heat is the output from electrical model. The junction temperature is the node

voltage equivalent thermal network, which can be simulated instantly with the same circuit simulator as for electrical model.

## Validation

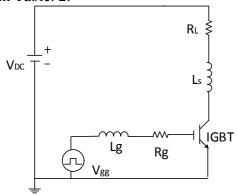

The physics-based electro-thermal model for FS IGBT is implemented in Matlab/Simulink, To validate the model, a commercial IGBT is selected for research in this study. This device is a kind of FS IGBT from International Rectifier and has a plastic package of TO-220AB. The validation chose the resistive-load circuit which is shown in Fig. 5 and the electrical parameters of the circuit are listed in Table. 2.

Table. 2 The electrical parameter of the circuit

| Parameter        | Unit | Value |  |  |

|------------------|------|-------|--|--|

| $V_{\rm gg}$     | V    | 15    |  |  |

| $L_{\mathrm{g}}$ | nН   | 33    |  |  |

| $R_{\mathrm{g}}$ | Ω    | 10    |  |  |

| $L_{ m s}$       | nН   | 150   |  |  |

| $R_{ m L}$       | Ω    | 2     |  |  |

Fig. 5 IGBT resistive-load circuit

Firstly, the parameters of the device need to be extracted as the input of the electro-thermal model [10]. The results of parameter extraction of selected FS IGBT are listed in Table. 3.

Table. 3 The results of parameter extraction of IRGB4059DPbF

| Parameter  | Unit               | Physical meaning               | Value                  |

|------------|--------------------|--------------------------------|------------------------|

| $V_{TH}$   | V                  | MOS threshold voltage          | 6.1                    |

| Кр         | AV <sup>-2</sup>   | MOS transconductance           | 0.42                   |

|            |                    | coefficient                    |                        |

| $C_{GE}$   | nF                 | gate-emitter capacitance       | 0.25                   |

| A          | cm <sup>2</sup>    | chip real estate               | 0.03696                |

| $a_i$      | -                  | the percentage of cells in the | 0.28922                |

|            |                    | whole chip.                    |                        |

| $C_{ox}$   | nFcm <sup>-2</sup> | oxide capacitor per area       | 8.279                  |

| $N_B$      | cm <sup>-3</sup>   | local doping concentration     | 3.279×10 <sup>14</sup> |

|            |                    | in the base region             |                        |

| $W_B$      | μm                 | metallurgical base width       | 70                     |

| $W_H$      | μm                 | the width of N type buffer     | 6                      |

|            |                    | layer                          |                        |

| $l_m$      | μm                 | intercell half-width           | 5                      |

| $	au_{HL}$ | μs                 | high-level injection carrier   | 0.287                  |

|            |                    | lifetime in N-base             |                        |

| $	au_{BF}$ | μs                 | high-level injection carrier   | 0.028                  |

|            |                    | lifetime in FS layer           |                        |

The conduction voltage is calculated by the presented electro-thermal model, and the comparison has been made with the experiment results. The results are shown in Table. 4, from which we can see that the simulation results and the experiment results meet a good agreement. So the physics-based electro-thermal model for FS IGBT which is presented in this paper is accurate.

Table. 4 The comparison between the simulation results and the experiment results

| Current Conduction voltage | 1A    | 2A    | 3A    | 4A    | 5A    | 6A    | 7A    |

|----------------------------|-------|-------|-------|-------|-------|-------|-------|

| Simulation                 | 1.31V | 1.68V | 1.98V | 2.24V | 2.49V | 2.74V | 2.98V |

| Experiment                 | 1.20V | 1.50V | 1.78V | 2.06V | 2.37V | 2.72V | 3.28V |

#### **Conclusions**

In this paper, a physics-based electro-thermal model for FS IGBT implemented in the Matlab/Simulink is proposed. The Fourier-based compact IGBT model is introduced to model the FS IGBT. The Cauer equivalent RC network is used to characterize the self-heat effect. The simulation and experiment results show great accord which proves that the model is accurate and efficient.

### References

- [1] Petar Igić, Nebojša Janković, Review of advanced IGBT compact models dedicated to circuit simulation, Electronics and Energetics, vol. 27-1 (2014) 13-23.

- [2] A.R. Hefner, D. L. Blackburn, Thermal Component Models for Electro-thermal Network Simulation, IEEE Transaction on Components, Packaging and Manufacturing Technology, vol. 17-A (1994) 413-424.

- [3] V. Szekely, A. Poppe, A. Pahi, A. Csendes, G. Hjas and M. Rencz, Electro-thermal and Logi-Thermal Simulations of VLSI Designs, IEEE Transactions on VLSI Systems, vol. 5 (1997) 258-269.

- [4] Hefner Jr, Allen R, Modeling buffer layer IGBT's for circuit simulation, IEEE Transaction on Power Electronics, vol. 10-2 (1995) 111-123.

- [5] X. Kang, A. Caiafa, E. Santi, J.L. Hudgins, P.R. Palmer, Characterization and modeling of high voltage field-stop IGBTs, IEEE Transactions on Industry Applications, vol. 39-4 (2003) 922-928.

- [6] P. R. Palmer, E. Santi, J. L. Hudgins, X. Kang, J. C. Joyce, and P. Y. Eng, Circuit simulator models for the diode and IGBT with full temperature dependent features, IEEE Transactions on Power Electronics, vol. 18-5 (2003) 1220-1229.

- [7] A. T. Bryant, P. R. Palmer, E. Santi, and J. L. Hudgins, Simulation and optimization of diode and insulated gate bipolar resistor interaction in a copper cell using MATLAB and Simulink, IEEE Transactions on Industry applications, vol. 43-4 (2007) 874-883.

- [8] B. Du, J.L. Hudgins, E. Santi, A.T. Bryant, P.R. Palmer, H.A. Mantooth, Transient electro-thermal simulation of power semiconductor devices, IEEE Transactions on power electronics, vol. 5-1 (2010) 237-248.

- [9] T.K. Gachovska, B. Du, J.L. Hudgins, E. Santi, Transient Electro-Thermal Modeling of Bipolar Power Semiconductor Devices, Morgan & Claypool, San Rafael, 2013.

- [10] Y. Tang, B. Wang, M. Chen, and B. L. Liu, Simulation model and parameter extraction of Field-Stop (FS) IGBT, Microelectronics Reliability, vol. 52 (2012) 2920-2931.