# **Design of a New High-precision Digital Frequency Meter**

Jiawei Liu<sup>1, a</sup> and Hongwei Zhang<sup>1, b</sup>

<sup>1</sup>Southwest University for Nationalities, School of Electrical and Information Engineering, Electrical Engineering & Automation Chengdu, Sichuan Province 610225 China

<sup>a</sup>201331006041@swun.cn, <sup>b</sup>759724337@qq.com

**Keywords:** Communication protocol; Equal precision frequency measurement; MCU; Finite state machine (FSM); Frequency meter

**Abstract.** In order to solve the problem of low speed of the equal precision digital frequency meter based on MCU and FGPA, this paper proposed a new communication protocol between MCU and FPGA, in which a 16-bit data bus was applied for data parallel transmission and the FSM was used to realize 32-bit data transmission within the FPGA; and meanwhile, in order to ensure the stability of the system and prevent the frequency measuring error arising from the protocol problems, the program used asynchronous FIFO as an alternate communication channel and defined the FIFO data transmission cycle, which ensured no data loss caused by FIFO overflow during the data transmission. The results show that all the functions can meet the requirement, which proves the effectiveness of the proposed program.

# 一种新型的高精度数字频率计设计

刘家玮 1, a, 张红伟 1, b

西南民族大学, 电气信息工程学院、电气工程及其自动化, 中国 四川省 成都市 610225

<sup>a</sup>201331006041@swun.cn, <sup>b</sup>759724337@qq.com

摘要:为了解决单片机和 FPGA 联合实现等精度数字频率计系统速度较慢的问题,提出了一种单片机和 FPGA 之间的新型通信协议,协议通过 16 位宽的数据总线进行数据并行传输,在 FPGA 内部用状态机实现 32bit 数据的传输,同时为了保证系统的稳定性,防止协议出现问题而导致系统出现测频错误,方案中利用异步 FIFO 作为备用的通信通道,并对 FIFO 定义了数据传输周期,保证在数据传输时不会因为 FIFO 的溢出而导致数据的丢失。测得的结果表明各项功能均达到要求,证明了该方案的有效性。

关键词:通信协议;等精度测频;单片机;状态机;频率计

## 1. 引言

频率测量不仅在工程应用中有着非常重要的地位,而且在高精度系统中处于核心地位。在传统的电子测量仪器中,频率仪可以准确的测量频率并显示被测信号的频谱,但测量速度较慢,示波器在进行频率测量时频率较低,误差较大,无法实时地跟踪捕捉到被测信号的频率变化。由于数字频率计的能正确地捕捉到被测信号的频率的变化,精度很高,所以在现在技术领域拥有非常广泛的应用。本设计中的频率计采用等精度测频的方法,使测频精度大大增加,同时选用 FPGA 作为数据处理单元的核心,保证了高速,宽范围的测频要求。而 32 位 STM32 单片机和 FPGA 联合使用则让整个系统更加稳定,准确。

# 2. 系统组成

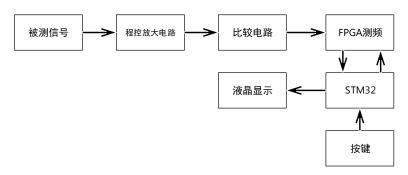

数字频率计的系统框图如图 1 所示,该系统主要包括程控放大电路、比较电路、FPGA 测频、单片机控制模块、显示模块和矩阵键盘模块。

图 1 频率计系统图

其中,程控放大电路和比较电路作为 FPGA 输入信号的前端调理电路,起到对小信号放大和对非方波信号整形的作用,测频电路是整个系统的核心,由 FPGA 实现,其中频率源由 FPGA 内部的数字 PLL 核来实现。单片机电路作为系统的控制核心,与 FPGA 通信,进而控制 FPGA 进行测频操作,同时读取测频数据,作进一步处理。键盘则是作为整个系统的外围控制单元,对系统整体进行控制。

### 3. 关键技术设计

### 3.1. 通信协议的设计

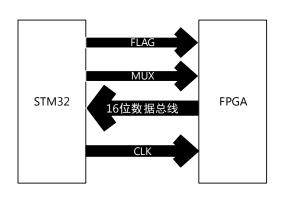

在这次设计的频率计中,我们为了加快频率计的系统速度,改进了单片机和 STM32 通信之间速度慢的问题,协议用的是我们自己设计的一个简单的通信协议。我们考虑到单片机的主频只有 76MHz,而我们所用的 FPGA 的主频有 100MHz,同时为了让频率计的测频结果的精度更高,我们利用数字锁相环技术将 FPGA 的频率倍频到 200MHz,所以如果用现有的通信协议无法较好的表现本系统快速,精确的优点。基于以上的考虑,我们自己定义了一套简单的通信协议,来配合我们频率计的要求。整个通信协议的流程图如图 2 所示

图 2 通信协议示意图

对于在传输链上,首先单片机发出一个 FLAG 信号,作为接受数据的请求信号,信号高电平有效。为了防止在接受到时钟信号时,数据端接收到无用的数据流信号,FPGA 在接收到请求以后先进行一秒的延时。同时单片机再发送一个选择的 MUX 信号,FPGA 识别后将相应的高位或者低位数据发送到数据缓冲器中,等待单片机的时钟信号到来。数据在时钟上升沿通过数据缓冲器传输出去。为了使数据的传输速度明显提高,将 32bit 的数据分成高 16 位和低 16 位,其中 MUX 信号是选择信号,在 MUX 信号为高电平的时候 FPGA 将高 16 位的数据送入数据缓冲器,MUX 信号为低电平时则将低 16 位数据送入数据缓冲器数据总线的宽度为16 位,这样传输完成 32 位的数据只需要两次时钟周期的时间即可完成。

### 3. 2. FIFO 的设计

我们在传输的时候为了防止自定义的通信协议出现数据丢失等问题,准备了 FIFO 作为备用的数据传输手段,在 FPGA 内部用异步 FIFO 作为接口,在 FIFO 的应用上,本设计充分考虑到时钟频率的差距,因此对 FIFO 周期化,每当传输了 512 个 16 位数据以后,将 FIFO 端

口的 full 信号拉高,等待单片机将 FIFO 中存储的数据读完,当单片机将 FIFO 内储存的数据 读完以后, empty 信号拉高, FPGA 将再次写入数据。FIFO 的周期即为 512。其中 FIFO 的 设计流程图如图 3 所示。

图 3 FIFO 流程图

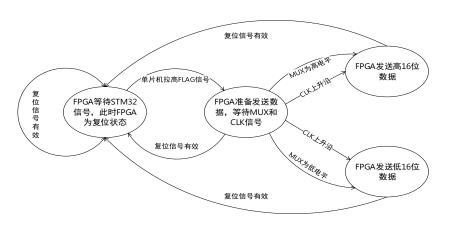

#### 3. 3. 系统内部状态机设计

状态机是这个频率计系统的核心,系统的状态机是用来根据不同条件来自动切换系统的状态。 本频率计系统共有四种状态,状态转移图如图 4 所示。

图 4 状态转移图

系统的初始状态是 FPGA 等待单片机的信号,当单片机将 FLAG 信号拉高,FPGA 准备发送 数据,同时等待 MUX 和 CLK 信号,在 CLK 信号上升沿来到的前提下,若 MUX 为高电平, 则 FPGA 将高 16 位的数据发出给单片机, 若 MUX 为低电平, FPGA 将低 16 位的数据发出给 单片机。系统在任何状态下,若复位信号有效,则系统回到最初始的状态。

### 4. 实验测试

#### 4. 1. 实验测试结果

使用仪器: 直流电源 APS30035-3D, 信号源 DG4072, 示波器 GDS-3502, 万用 FLUKE 117C 依次测试各个模块的电压输入、输出;输入信号幅度和频率以及输出信号幅度和频率。我们 为了检测频率计的性能,分别测试了在输入的正弦波频率为 1Hz、10kHz、1MHz、10MHz、 100MHz 不同的 5 种频率时得到的实验结果。其中表 1 是在输入信号电压的均方根值等于 10mv 的条件下测得的结果, 表 2 是在输入信号电压的均方根值等于 500mv 的条件下测得的 结果。

表 1 频率测量(Vrms=10mv)

| 输入值(HZ) | 测试值(HZ)     | 相对误差(%)  |

|---------|-------------|----------|

| 1       | 1.000091    | 0. 0091  |

| 10K     | 9.999989K   | 0.0011   |

| 1M      | 1.0000266M  | 0. 00266 |

| 10M     | 9.999951M   | 0. 0049  |

| 100M    | 100.000107M | 0.0107   |

表 2 频率测量 (vpp=500mv)

| 输入值(HZ) | 测试值(HZ)     | 相对误差(%) |

|---------|-------------|---------|

| 1       | 1.000011    | 0.0011  |

| 10K     | 10.000089K  | 0.0089  |

| 1M      | 1.0000006M  | 0.006   |

| 10M     | 10.000031M  | 0.0031  |

| 100M    | 100.000107M | 0. 0107 |

实验结果表明系统对频率测量的相对误差小于 0.01%, 在理论分析中提到系统中的高频标准脉冲的计数可能会产生±1 的误差, 但是由于我们采用 200M 的高频脉冲, 在闸门时间为 1s 的情况下, 误差可以控制在 0.01% 以内。我们测试的结果也证实了这一点。

### 5. 结语

本文提出了一种新的方法来实现频率计,用自己设计的一套通信协议来实现系统内部 FPGA 和 STM32 进行通信,加快了 FPGA 和单片机通信之间的速度。在当今可编程逻辑器件发展飞速的今天,使得基于 FPGA 的数字频率计有更大的发展空间,相信随着信息技术的不断发展,基于 FPGA 和单片机的频率计会有更广阔的市场。

### 参考文献

- [1] 方易圆, 邓琛. 等精度频率计的 FPGA 设计[J]. 测控技术, 2012, 31(10):1-4.

- [2] 陈景波, 丁旭, 江维勇. 基于 FPGA 的等精度数字频率计的设计[J]. 常熟理工学院学报, 2011, 25(8):90-93.

- [3] 梁颖, 佟川. 基于 FPGA 的等精度频率计单片系统设计[J]. 软件, 2012, 33(1):49-51.

- [4] 董灵灵. 数字频率计设计[C]// 云南电力技术论坛. 2011.

- [5] 高扬. 基于 EPM7128SLC84-15 的 CPLD 数字频率计的硬件开发设计[C]// 中国职协 2013 年度优秀科研成果获奖论文集. 2013:89-89.

- [6] Wang P, Yan C J, Niu T, et al. Frequency Meter with Equal Precision Based FPGA + MCU[J]. Applied Mechanics & Materials, 2014, 614:308-311.

- [7] Zhang C, Meng X B. Design of Digital Frequency Meter Based on FPGA [J]. Computer Knowledge & Technology, 2014.

- [8] Wei-Bing L I, Dao-Tong L I, Bo H U, et al. Design of multi-functional frequency meter based on FPGA [J]. Electronic Design Engineering, 2012

- [9] Fang Y Y, Chen D. Design of Equal Precision Frequency Meter Based on FPGA [J].

- Engineering, 2012, 04(10):1-4...

- [10] Zhang W, Cui S, Qi J, et al. Design of High Precision Frequency Meter Based on SOPC[C]// First International Conference on Instrumentation, Measurement, Computer, Communication and Control. IEEE, 2011:566-569.

### References

- [1] Fang Yi yuan, Deng Chen. FPGA design of equal precision frequency meter [J]. Measurement and control technology, 2012, 31 (10): 1-4.

- [2] Chen Jingbo, Ding Xu, Jiang Weiyong. Design of equal precision digital frequency meter based on FPGA [J]. Journal of Changshu Institute of Technology, 2011, 25 (8): 90-93.

- [3] Liang Ying, Tong Chuan. Design of a single chip system based on FPGA and other precision frequency meter [J]. Software, 2012, 33(1):49-51.

- [4] Dong Lingling. Design of digital frequency meter[C]// Yunnan Electric Power Technology Forum.2011

- [5] [5] EPM7128SLC84-15[C]// China Association for the year 2013 outstanding achievements in scientific research papers. 2013:89-89.

- [6] Wang P, Yan C J, Niu T, et al. Frequency Meter with Equal Precision Based FPGA + MCU [J]. Applied Mechanics & Materials, 2014, 614:308-311.

- [7] Zhang C, Meng X B. Design of Digital Frequency Meter Based on FPGA [J]. Computer Knowledge & Technology, 2014.

- [8] Wei-Bing L I, Dao-Tong L I, Bo H U, et al. Design of multi-functional frequency meter based on FPGA [J]. Electronic Design Engineering, 2012

- [9] Fang Y Y, Chen D. Design of Equal Precision Frequency Meter Based on FPGA [J]. Engineering, 2012, 04(10):1-4..

- [10] Zhang W, Cui S, Qi J, et al. Design of High Precision Frequency Meter Based on SOPC [C]// First International Conference on Instrumentation, Measurement, Computer, Communication and Control. IEEE, 2011:566-569.

作者简介: 刘家玮(1995—), 男,河南,本科,数字信号处理,201331006041@swun.cn。