# Design of CMOS Dual-band Reconfigurable Low Noise Amplifier for Radar T/R Module

Zhangfa Liu\* and Jiaqian Wu School of Electronic Information and Engineering, Beijing Jiaotong University, Beijing, China \*Corresponding author

Abstract—A dual-band reconfigurable noise amplifier(LNA) for T/R module is designed based on SMIC 65nm CMOS process In this paper, the low noise amplifier can operate in L/S band optionally. The simulation results shown it has a larger than 20dB gain and smaller than 2.5dB noise figure for both L and S bands, the IP3 is bigger than -8dBm, the layout of low noise amplifier occupies 1750um\*1000um area.

Keywords—reconfigurable; low Noise amplifier; CMOS; dualband

#### I. Introduction

Currently, the reconfigurable miniaturized terminals are widely employed in various wireless applications; the different standards or frequency ranges as well as the different signal and modules are used in transceiver, meanwile, in order to increase battery life, the minimum power consumption is required[1]-[2]. For example, in some cases, CMOS transceiver modules need to be freely switched between frequency bands. Traditional concurrent or multiple independent T/R solutions are not necessarily the best choice. Choosing a reconfigurable circuit solution may be more advantageous. The configurable LNA is a key component for the configurable T/R module.

A design and simulation results of the configurable low noise amplifier based on 65nm CMOS process and .5-V operation for T/R module is proposed in this paper. The circuit of configurable of LNA achieves the following sufficient characteristics: more than -8dBm IIP3, smaller than 2.5dB noise figure, more than 20dB gain for the LNA.

The construction of the paper is as follows. Section II makes a brief description of the circuit analysis and design. Section III presents the simulation results of S-parameter, noise figure, gain and IP3 for configurable LNA at L- and Sband respectively, and the layout of the LNA is also provided in this section. Section IV provides a performance summary for this LNA.

#### CIRCUIT DESIGN AND ANALYSIS

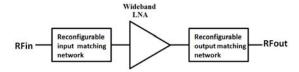

Reconfigurable low noise amplifier designs now have two main approaches: one is to use a wideband input matching network, then a narrowband tuning structure is used in the output network [1],[3]; the other is to use the tuning circuits at both the input and output [3]-[4]. The first method can use a common-gate amplifier or use a filter to cover the L-band and S-band, but the noise caused by the common-gate amplifier is not employed in this paper, and it is unrealistic for the loworder filter to achieve a bandwidth of larger than 2 GHz.

The diagram of typical Reconfigurable LNA is shown in the Figure 1, it consist of a reconfigurable input matching network, wideband LNA and one reconfigurable output matching network.

FIGURE I. DIAGRAM OF TYPICAL RECONFIGURABLE LNA

# A. Input Matching Network

At the front-end in a reconfigurable receiver, the low-noise amplifier is required to have the characteristics of good input impedance matching, high voltage gain, high linearity, low power consumption and low noise figure in dynamically designated frequency ranges. The frequency selection performance of this kind of LNA can be achieved by using concurrent multiband or tunable single band solutions.

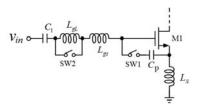

The proposed input matching network of the configurable LNA is shown as the following Figure 2, where C<sub>1</sub> is a large DC block capacitor and Cp is used to expand the degree of choose freedom of the circuit and reduce the value of the gate inductance. When the switch SW2 is on while SW1 is off, it can be have:

FIGURE II. THE INPUT MATCHING NETWORK

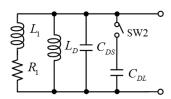

FIGURE III. THE OUTPUT MATCHING NETWORK

$$Z_{in} = s(L_{gs} + L_s) + \frac{1}{sC_{gs1}} + \frac{g_{m1}}{C_{gs1}}L_s$$

(1)

Where  $C_{gsI}$  is the gate-source capacitance of the input transistor M1, in the equation (1), the real part of the  $Z_{in}$  is matched to 50  $\Omega$ , so the value  $L_{gs}$  can be obtained. The resonant frequency of the matching network can be obtained as follow:

$$\omega_0 = \frac{1}{\sqrt{(L_{gs} + L_s)C_{gs1}}}$$

(2)

Chose the appropriate  $L_{\rm gs}$  allows the circuit to operate in the S-band.

When SW2 is off while SW1 is on, it can be obtained:

$$Z_{in} = s(L_{gs} + L_{gL} + L_s) + \frac{1}{sC_{total}} + \frac{g_{m1}}{C_{total}}L_s$$

(3)

Where

$$C_{total} = C_p + C_{gs1} \tag{4}$$

In this case the resonant frequency of the matching network can be obtained as:

$$\omega_0 = \frac{1}{\sqrt{\left(L_{gs} + L_{gL} + L_s\right)C_{total}}} \tag{5}$$

The real part of the  $Z_{in}$  is matched to  $50\Omega_{\text{\tiny P}}$  so it can be obtained:

$$\frac{g_{m1}}{C_{total}}L_s = 50 \tag{6}$$

Chose the appropriate  $C_p$  allows the circuit to operate in the L-band.

# B. Output Matching Network

The output matching network adds a parallel peaking inductor to expand the bandwidth based on the traditional RLC parallel resonant tank. The output matching network circuit diagram is shown in above Figure 3.

According to the shunt peaking technique, the resonant frequency is:

$$\omega_0 = \omega_{L/S} \sqrt{\left(-\frac{m^2}{2} + m + 1\right) + \sqrt{\left(-\frac{m^2}{2} + m + 1\right)^2 + m^2}}$$

(7)

Where

$$m = \frac{R_1 C_{DS}}{L_1 / R_1} \tag{8}$$

$\omega_{L/S}$  is the operation frequency depending on whether SW2 is on or off.

*m* is chosen to be 1.41 to obtain the widest bandwidth.

When SW2 is off, the circuit operates in S-band, and:

$$\omega_{S} = \frac{1}{\sqrt{L_{D}C_{DS}}} \tag{9}$$

Then choose appropriate values of  $C_{DS}$ ,  $L_D$  and  $L_I$  can make the circuit operates in S band.

When SW2 is on, then:

$$\omega_L = \frac{1}{\sqrt{L_D(C_{DS} + C_{DL})}} \tag{10}$$

Then choose appropriate value of CDL can make the circuit operates in L band.

### C. Noise Analysis

The noise figure expression given by the classical noise theory is as follows:

$$F = F_{min} + \frac{R_n}{G_s} \left[ \left( G_s - G_{opt} \right)^2 + \left( B_s - B_{opt} \right)^2 \right]$$

(11)

The parameters in the above equation are related to power consumption. The power consumption is used to describe these items as follows:

$$I_D = WLC_{ox} V_{sat} E_{sat} \frac{\rho^2}{1+\rho}$$

(12)

Where

$$v_{sat} = \frac{\mu_n}{2} E_{sat}$$

,  $\rho = \frac{V_{gs} - V_{th}}{L E_{sat}} = \frac{V_{od}}{L E_{sat}}$

Therefore, the power consumption can be written as:

$$P_D = V_{DD}I_D = V_{DD}WLC_{ox} V_{sat}E_{sat} \frac{\rho^2}{1+\rho}$$

(13)

Using the above expression, the noise figure can be redescribed with  $\rho$  and  $P_D$ . Finding the minimum value of the obtained equations are a sufficiently complex problem. If the working condition is not in the case of high power, then the minimum noise figure occurs when the following equation holds:

$$\rho^{2} \approx \frac{P_{D}}{P_{0}} \sqrt{\frac{\delta}{5\gamma} (1 - \left| c \right|^{2})} [1 + \sqrt{\frac{7}{4}}]$$

(14)

Then the value  $Q_s$  when the minimum noise figure is reached under power constraints is:

$$Q_{sp} = \left| c \right| \sqrt{\frac{5\gamma}{\delta}} \left[ 1 + \sqrt{1 + \frac{3}{\left| c \right|^2}} \left( 1 + \frac{\delta}{5\gamma} \right) \right]$$

(15)

Once  $Q_{sp}$  is determined, an expression of the optimal device width can ultimately be derived:

$$W_{opt.p} = \frac{3}{2} \frac{1}{\omega L C_{ox} R_s Q_{sp}} \approx \frac{1}{3\omega L C_{ox} R_s}$$

(16)

For devices with a width  $W_{opt,p}$ , the noise figure obtained over the power constraints is:

$$F_{min.p} \approx 1 + 2.4 \frac{\gamma}{\alpha} \left[ \frac{\omega}{\omega_T} \right]$$

(17)

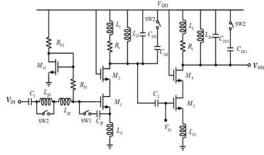

Finally the proposed dual-band configurable low noise amplifier is shown in Figure 4.

FIGURE IV. PROPOSED DUAL-BAND RECONFIGURABLE LNA

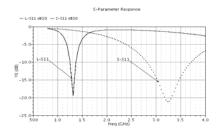

### III. SIMULATION RESULTS OF PERFORMANCE

The S11 simulation performance of the dual-band configurable LNA is shown in Figure 5. It can be found that S11 has a peak at about 1.3 GHz (about -19 dB) in L-band. In the frequency range (1.2 GHz to 1.4 GHz), the value of S11 is about It is -19dB~-10dB. In S-band S11 has a peak at about 3.25 GHz (about -21 dB).

FIGURE V. S11 PARAMTERS OF THE LNA IN L/S BAND

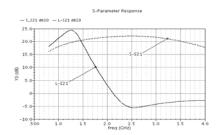

FIGURE VI. S21 PARAMETERS OF THE LNA IN L/S BAND

The gain simulation results of the dual-band reconfigurable low-noise amplifier are shown in Figure 6. In L-band S21 parameter is close to 25 dB at the center frequency (1.3 GHz) and the gain is more than 20 dB in the 200 M bandwidth.

It can also be seen from Figure 6 that in S-band the gain reaches 22dB at the maximum, and in the range of 3.0GHz~3.4GHz, the S21 value is 20dB~22dB,

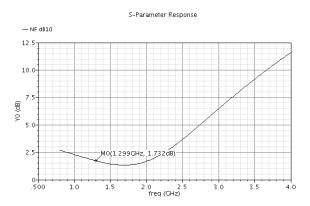

The noise figure(NF) simulation result of the dual-band reconfigurable low-noise amplifier is shown in Figure 7 and Figure 8. The center frequency point of NF in L-band deviates to the right. At the frequency point (1.3 GHz), the value is 1.732 dB. Within the frequency range, both are less than 2dB.

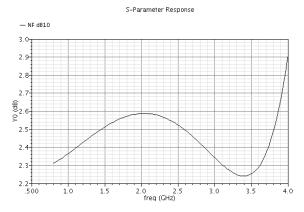

In S-band, the NF simulation result is shown in Figure 8. The value of NF is the minimum value 2.25 dB IS at 3.35 GHz. The value of NF is slightly higher than the 2 dB IN in the specific frequency range. The reason for this result is mainly that the MOS switch is used. The MOS switch can be used as a noise source in the case of conduction. At the same time, the parasitic parameters and on-resistance brought by the switch make the noise of the circuit larger than that of the single frequency band deterioration.

FIGURE VII. NF OF THE RECONFIGURABLE LNA IN L-BAND

FIGURE VIII. NF OF THE RECONFIGURABLE LNA IN S-BAND

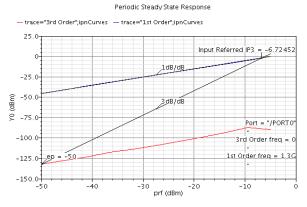

The IIP3 simulation performance in L-band is shown in Figure 9. At the specified frequency point, the value of IIP3 is -6.72dBm, which is better than -10dBm. However, due to the employment of the two-stage structure, the value of IIP3 is greater than the value of the single-band.

FIGURE IX. IIP3 OF THE RECONFIGURABLE LNA IN L-BAND

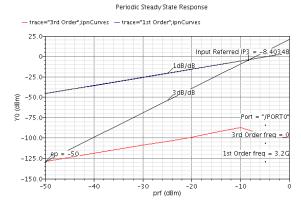

The IIP3 simulation performance in S-band IIP3 is shown in Figure 10. At the specified frequency (3.2 GHz), the IIP3 value is also reduced compared to the single-band, the value of is approximately -8.40 dBm.

FIGURE X. IP3 OF THE RECONFIGURABLE LNA IN S-BAND

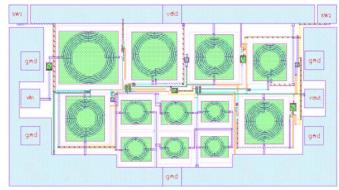

Finally, the layout of the configurable LNA is presented as in Figure 11, the area is 1750um\*1000um.

FIGURE XI. LAYOUT OF THE PROPOSED DUAL-BAND RECONFIGURABLE LNA

In the layout, the SW1 and SW2 are the two switches, when SW1 is on while SW2 is off, the circuit operates in L-band, and when SW1 is off while SW2 if on, the circuit will work in S-band.

### IV. CONCLUSIONS

A dual-band configurable LNA is presented in this paper, the simulation results shown that the LNA has 25dB and 22dB of gain, 1.7dB and 2.2dB of noise figure, -6.7dBm and -8.4dBm at 1.3GHz and 3.2GHz respectively. The layout of the LNA occupies 1750um\*1000um area.

#### REFERENCES

- [1] Chang-Tsung Fu, Chun-Lin Ko, Chien-Nan Kuo, and Ying-Zong Juang, "A 2.4–5.4-GHz Wide Tuning-Range CMOS Reconfigurable Low-Noise Amplifier," IEEE Trans. Microw. Theory Tech., vol. 50, no. 1, pp. 288–301, Jan. 2002.

- [2] Nathan M. Neihart, Jeremy Brown, and Xiaohua Yu, "A Dual-Band 2.45/6 GHz CMOS LNA Utilizing a Dual-Resonant Transformer-Based Matching Network," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 59, no. 8, pp. 1743–1751, Aug. 2012.

- [3] Xiaohua Yu, and Nathan M. Neihart, "Analysis and Design of a Reconfigurable Multimode Low-Noise Amplifier Utilizing a Multitap Transformer," IEEE Trans. Microw. Theory Tech., vol. 61, no. 3, pp. 1236–1246, March 2013.

- [4] K.-H. Chen and S.-I. Liu, "Inductorless wideband CMOS low-noise amplifiers using noise-canceling technique," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 59, no. 2, pp. 305–314, Feb. 2012.

- [5] J. Borremans, P. Wambacq, and D. Linten, "An ESD-protected DC-to-6 GHz 9.7 mW LNA in 90 nm digital CMOS," in IEEE ISSCC Tech. Dig., 2007, pp. 422–423.

- [6] Y.-C. Yang, P.-W. Lee, H.-W. Chiu, Y.-S. Lin, G.-W. Huang, and S.-S. Lu, "Reconfigurable SiGe low-noise amplifier with variable miller capacitance," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 53, no. 12, pp. 2567–2577, Dec. 2006.

- [7] M. Battista, J. Gaubert, M. Egels, S. Bourdel, and H. Barthelemy, "High-voltage-gain CMOS LNA for 6–8.5-GHz UWB receivers," IEEE Trans. Circuits Syst. II, Expr. Briefs, vol. 55, no. 8, pp. 713–717, Aug. 2008

- [8] Y. Lu, K. S. Yeo, A. Cabuk, J. G. Ma, M. A. Do, and Z. H. Lu, "A novel CMOS low-noise amplifier design for 3.1-to-10.6-GHz ultrawide-band wireless receivers," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 53, no. 8, pp. 1683–1692, Aug. 2006.

- [9] P. Simitsakis, Y. Papananos, and E. S. Kytonaki, "Design of a low voltage-low power 3.1–10.6 GHz UWB RF front-end in a CMOS 65nm technology," IEEE Trans. Circuits Syst. II, Expr. Briefs, vol. 57, no.11, pp. 833–837, Nov. 2010.

- [10] H. R. Wang, L. Zhang, and Z. P. Yu, "A wideband inductorless LNA with local feedback and noise cancelling for low-power low-voltage applications," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 57, no. 8, pp. 1993–2005, Aug. 2010.

- [11] A.Meaamar, C. C. Boon, K. S. Yeo, andM. A. Do, "A wideband low power low-noise amplifier inCMOS technology," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 57, pp. 773–782, Apr. 2010.

- [12] C. T. Fu, C. L. Ko, C. N. Kuo, and Y. Z. Juang, "A 2.4–5.4-GHz wide tuning-range CMOS reconfigurable low-noise amplifier," IEEE Trans. Microw. Theory Tech., vol. 56, no. 12, pp. 2754–2763, Dec. 2008.

- [13] Nathan M. Neihart, Jeremy Brown, and Xiaohua Yu, "A Dual-Band 2.45/6 GHz CMOS LNA Utilizing a Dual-Resonant Transformer-Based Matching Network," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 59, no. 8, pp. 1743–1751, Aug. 2012.

- [14] E. Duvivier, G. Puccio, S. Cipriani, L. Carpineto, P. Cusinato, B. Bisanti, F. Galant, F. Chalet, F. Coppola, S. Cercelaru, N. Vallespin, J. C. Jiguet, and G. Sirna, "A fully integrated zero-IF transceiver for GSM-GPRS quad-band application," IEEE J. Solid-State Circuits, vol. 38, no. 12, pp. 2249–2257, Dec. 2003.

- [15] H. Sjoland, A. Karimi-Sanjaani, and A. A. Abidi, "A merged CMOS LNA and mixer for WCDMA receiver," IEEE J. Solid-State Circuits, vol. 38, no. 6, pp. 1045–1050, Jun. 2003.

- [16] Xiaohua Yu, and Nathan M. Neihart, "Analysis and Design of a Reconfigurable Multimode Low-Noise Amplifier Utilizing a Multitap Transformer," IEEE Trans. Microw. Theory Tech., vol. 61, no. 3, pp. 1236–1246, March 2013.

- [17] Z. Ru, N. A. Moseley, E. A. M. Klumperink, and B. Nauta, "Digitally enhanced software-defined radio receiver robust to out-of-band interference," IEEE J. Solid-State Circuits, vol. 44, no. 12, pp. 3359– 3375. Dec. 2009.

- [18] K.-H. Chen and S.-I. Liu, "Inductorless wideband CMOS low-noise amplifiers using noise-canceling technique," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 59, no. 2, pp. 305–314, Feb. 2012.