# Online Monitoring of MOS Junction Temperature in Power Cycle Test

Boyang Jiang, Chunsheng Guo\* and Lin Luo

Faculty of Information Technology, Beijing University of Technology, Beijing 100124, China

\*Corresponding author

Abstract—The power cycle test is an important method to test the reliability of the device and eliminate unqualified samples. It is significance to measure various performance of the device. However, the junction temperature of the device changes greatly during the power cycle. Inappropriate high power cycle and duty cycle will make the junction temperature of the device too high, which can directly affect the experimental results and bring about economic losses. Therefore, this paper proposes an online monitoring method of MOS junction temperature during power cycle process, which can effectively prevent the device junction temperature from being too high and at the same time provide an objective basis for the selection of power cycle and duty cycle.

Keywords—power cycle test; junction temperature; online

### I. INTRODUCTION

In the power cycle test, the large pulse power is applied to the device under test, causing the junction temperature of the device to be in an alternating shift of gradually increasing and continuously decreasing, which becomes an important index to evaluate the reliability of the device under test. However, it is very difficult to have a uniform standard for the rated power and power cycle applied due to different devices and different heat dissipation platforms.

Excessive power or prolonged cycle will cause the junction temperature of to exceed the limited temperature, which will affect the reliability of the test results and bring about the risk of thermal failure. Based on the above problem, in this paper, the change of MOS junction temperature during power cycle is monitored online by selecting appropriate temperature sensitive electrical parameters (TSEPs) using electrical method [1]. In order to avoid the interference of test parameters on the power cycle experiment itself, no additional test electrical signals are introduced in the junction temperature test process.

In order to meet the requirements of online monitoring of the junction temperature of MOS devices, the power cycle circuit and the library of temperature calibration curve are optimized.

## II. SELECTING TEMPERATURE SENSITIVE PARAMETERS

Selection the TSEPs of MOS devices, many scholars have put forward some useful schemes <sup>[2-3]</sup> in the world, such as, threshold voltage mentioned by H. Chen, V. Pickert <sup>[4]</sup> and switching current studied by A. Castellazzi <sup>[5]</sup>. However, the above researchers focused on the junction temperature measurement or the introduction of test signals under on-state of

MOS devices, which cannot achieve the trend of online monitoring of junction temperature rise and temperature drop under the power cycle condition. In order to solve this problem, through improving the power cycle test circuit, TSEPs are selected in the power application process and the cut-off process respectively, in order to realize the junction temperature monitoring in the whole power cycle.

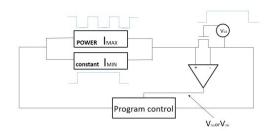

During the power cycle, the  $V_{GS}$  voltage is constant, two current sources apply a constant current signal to the source and drain of the device, one of which is the power signal  $I_{MAX}$  and the other is the temperature drop test signal  $I_{MIN}$ . Since  $I_{MAX}{>>}I_{MIN}$ ,  $I_{MAX}$  and  $I_{MIN}$  can each correspond to an independent TSEP  $V_{DS}$ .

When the device is applied with a power, two current sources work at the same time:  $P = I_{MAX} * V_{DS1}$ . At this time,  $V_{DS1}$  can be used as a TSEP to measure the temperature rise curve of the device. When the power is turned off, the current source is also turned off. The temperature drop curve can be tested by  $V_{DS2}$  that is as the TSEP. Since the gate voltage of the MOS is constant throughout the power cycle, the gate voltage cannot be used as an independent TSEP. The test equipment is shown in Fig.1.

FIGURE I. TEMPERATURE CALIBRATION CURVE TESTING EQUIPMENT

$$I_{DS} = \beta [(V_{gs} - V_T)V_{DS} - \frac{1}{2}V_{DS}^2]$$

(1)

Since the device operates in the linear region under actual operating conditions, equation (1) can be simplified as follows:

$$I_{D} = \beta (V_{gs} - V_{T})V_{DS}$$

(2)

$I_{DS}$  is drain-source current,  $V_{DS}$  is drain-source voltage,  $V_{GS}$  is gate-source voltage,  $V_{T}$  is threshold voltage, and  $\beta$  is called gain factor:

$$\beta = \frac{\mu_n C_{OX} W}{L} \tag{3}$$

Where  $C_{OX}$  represents the gate oxide capacitance per unit area, W represents the channel width, L represents the channel length, and  $\mu_n$  is called carrier mobility. For equation (2), there are two temperature-related parameters, carrier mobility  $\mu_n$  and threshold voltage  $V_T$ :

$$\mu_{n} = \mu_{n}(T_{0}) \times (\frac{T_{0}}{T})^{2} \tag{4}$$

$$\mathbf{V}_{\mathbf{T}} = \mathbf{V}_{\mathbf{T}}(\mathbf{T}_{\mathbf{0}}) + \Pi(\mathbf{T} - \mathbf{T}_{\mathbf{0}}) \tag{5}$$

For MOS devices, some studies show that P < 0

After finishing formula (2), you can get:

$$\frac{t_0}{v_{DS}} = \frac{\mu_{\rm B}(T_0) \times T_0^{-2} C_{\rm OX} W}{L T^2} ([V_{\rm GS} - V_{\rm T}(T_0) + PT_0] - PT)])$$

(6)

In order to simplify the mathematical model, if  $\underline{\underline{\mu_n(T_0)} \times T_0} = C_{ON} \underline{W} = Y$ ,  $[V_{GS} - V_T(T_0) + PT_0] = A$ , Y and K are two constant quantities independent of temperature. A < 0 when the  $V_{GS}$  is smaller and A > 0 when the  $V_{GS}$  is larger. In the linear region, the ratio of  $\underline{V_{DS}}$  is a constant value under the same gate voltage and temperature conditions, which can make  $\underline{V_{DS}} = R_{om}$ . Then, according to the above description, it can be obtained:

$$P_{o\mu} = Y \frac{A - PT}{T^2} \tag{7}$$

Available for sorting:

$$P_{o\mu} = \frac{AY}{T^2} - \frac{PY}{T} \tag{8}$$

Because P < 0, the  $R_{om}$  drops with temperature T rising, and the linear region shows that the slope of the straight line decreases with temperature rising, and the change trend is absolutely monotonous, and the temperature calibration curve shows that there is no influence of temperature blind area.

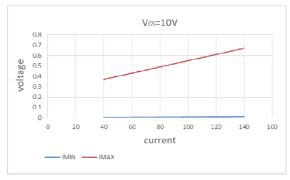

# III. PRINCIPLE OF POWER CYCLE CIRCUIT AND TEMPERATURE CALIBRATION CURVE

In the application process, only two temperature calibration curves need to be constructed in advance under the specific gate voltage  $V_{\rm GS}$ , namely  $V_{\rm DS2}$ –T under the  $I_{\rm MAX}$  condition and  $V_{\rm DS1}$ –T under the  $I_{\rm MIN}$  condition. The constant current measurement mode can be used when the power is small under the  $I_{\rm MIN}$  condition. The pulse test method must be used to avoid self-heating under the  $I_{\rm MAX}$  condition. The test process and results are shown in figure 2 and figure 3.

FIGURE II. SCHEMATIC DIAGRAM OF POWER CYCLE PRINCIPLE

FIGURE III. TEMPERATURE CALIBRATION CURVE DURING POWER CYCLE PROCESS

When power is applied, the first temperature calibration curve can be used to monitor the temperature rise. Under the power off-state, the second temperature calibration curve can be used to monitor the temperature drop trend. In the power application process, the test current source provided the small signal, which has no influence on the working circuit. In the off process, the off-state of the power current source does not interfere with the test signal. Therefore, the above two reasons perfectly realize the aim of non-interference in online acquisition of TSEPs during power cycle.

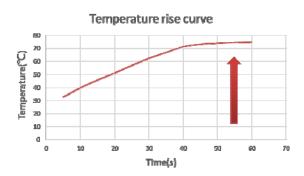

FIGURE IV. SCHEMATIC DIAGRAM OF TEMPERATURE RISE CURVE

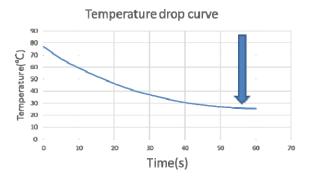

FIGURE V. SCHEMATIC DIAGRAM OF TEMPERATURE DROP CURVE

During power cycle, online monitoring of the temperature rise process and the temperature drop trend have important significance. The junction temperature of the power-induced device increases, and the junction temperature increase causes the load voltage to increase under the constant current condition. thus forming a positive feedback effect of power increase junction temperature rise - power increase, and the device is easily burnt out of control when the heat dissipation condition is poor. Monitoring the temperature rise state can effectively prevent the failure risk caused by too high junction temperature in time and prevent the junction temperature from being too high in advance. When the power is cut off, the device enters the heat dissipation process, and the too short heat dissipation time will lead to the initial junction temperature of the device not fully cooled when the next power cycle arrives, which will also easily lead to thermal failure.

The temperature rise curve is helpful to control the power cycle and the upper limit of the single power application time avoids the risk of high temperature. The temperature drop curve provides an objective basis for limiting the duty cycle to ensure that the device has enough cooling time to go through the next power cycle under test. Avoiding the influence of too high junction temperature on the experimental results will ensure that the test results obtained by the power cycle experiment are more effective, and at the same time avoid the economic loss caused by high temperature loss, thus having a broad application prospect in engineering.

## IV. CONCLUSION

Aiming at the problem of online monitoring of junction temperature in power MOS device power cycle experiments, through reasonable matching of experimental circuits and selection of appropriate TSEPs, the junction temperature of the device can be measured online without any interference with experimental conditions, and then simplifying the temperature calibration curve and making it more convenient for practical engineering applications. Monitoring the MOS junction temperature is helpful for engineers to master the junction temperature of device, which can avoid failure caused by excessive power and long time, effectively limit the power cycle and duty cycle in the power cycle process, eliminate the influence caused by high temperature damage, and ensure that the experimental results are more accurate and reliable.

#### REFERENCES

- [1] A. Griffo, J. Wang, K. Colombage and T. Kamel, "Real-Time Measurement of Temperature Sensitive Electrical Parameters in SiC Power MOSFETs," in IEEE Transactions on Industrial Electronics, vol. 65, no. 3, pp. 2663-2671, March 2018.

- [2] D-L. Blackburn, D-W. Berning, "Power MOSFET temperature measurements", Annual Power Electronics Specialists Conference, pp. 400-407, Cambridge, Massachussets, USA, June 14-17, 1982.

- [3] J. Zarebski K. Gorecki "The electrothermal large-signal model of power MOS transistors for SPICE" IEEE Trans. Power Electron. vol. 25 no. pp. 1265-1274 May 2010.

- [4] H. Chen, V. Pickert, D.J. Atkinson, L.S. Pritchard, "On-line monitoring of the MOSFET device junction temperature by computation of the threshold voltage", The 3rd IET International Conference on Power Electronics, Machines and Drives, pp. 440-444, Dublin, Ireland, Apr. 4-6,2006

- [5] A. Castellazzi, G. Wachutka, "Low-voltage PowerMOSFETs used as dissipative elements: electrothermal analysis and characterization", 37th IEEE Power Electronics Specialists Conference, pp. 1-7, Jeju, Korea, June 18-22, 2006.