# The Advanced Carrier Based Pulse Width Modulation Using Third Injection Harmonic Reference Signal on Neutral Point Clamped Inverter

I. Ketut Wiryajati<sup>(⊠)</sup>, I. N. Wahyu Satiawan, I. B. Fery Citarsa, I. M. Budi Suksmadana, and Supriono

Department of Electrical Engineering, University of Mataram, Mataram, Indonesia kjatiwirya@unram.ac.id

**Abstract.** This paper proposes development of a Pulse Width Modulation (PWM) scheme that overcomes the weakness of conventional Carrier-Based PWM (CBPWM) performance on Neural Point Clamp Inverter (NPC). This scheme uses the conventional CBPWM technique to developed Advanced CBPWM. This technique uses triangular carriers in different amplitudes that are arranged in composition, then injects the modulated signal that has been decomposed with the third harmonic. The proposed PWM schema was verified using MATLAB/Simulink software. By applying this scheme, the quality of power, voltage and current are improved, and finally Total Harmonic Distortion (THD) can be reduced.

Keywords: Neural Point Clamp Inverter  $\cdot$  CBPWM  $\cdot$  NPC  $\cdot$  inverter  $\cdot$  THD  $\cdot$  Advance CBPWM

#### 1 Introduction

Multilevel inverter is one of the electronic devices that is very well known in the electric power systems application and in industry. Since multilevel inverter has high performance and produces low harmonics [1–3]. There are several types of multilevel inverters such as Neutral Point Clamped, (NPC) Flying Capacitor Inverters. In particular, the Neutral Point Clamped (NPC) converter is generally used at high voltages industry [4–7].

In conventional inverters, increasing the voltage level will increase the number of diodes, as well as for inverters using capacitors. In addition, the increase of voltage level causes higher cost and increasing of voltage unbalanced problem due to the use more diode or capacitor. Furthermore, the switching losses on the switches will also increase. However, Multilevel NPC inverters have advantages and disadvantages over the other inverters, because it no longer requires balancing on the diode or capacitor, this method only requires a separate dc voltage on each H-Bridge Inverter [8–10].

In this paper, an NPC inverter is used discussed. NPC will apply the proposed new modulation technique. The first development of a multilevel inverter was the NPC Inverter (INPC), this is because the topology has the following advantages:

- 1. The performance and waveform of the inverter is better especially at the fundamental frequency.

- 2. The use of capacitors can be charged first before being operated

- 3. The voltage level is very dependent on the capacitor voltage, namely in terms of voltage balance.

There are several modulation techniques to control the inverters. Such as Selected Harmonic Elimination (SHE) or Optimized Harmonic Stepped Waveform (OHSW), Space Vector PWM (SVPWM), and Carrier Based PWM (CBPWM) [11–13]. Among these modulation techniques, the easiest to apply to multilevel inverters is the CBPWM modulation technique. Although CBPWM technique is very easy to implement, there are several challenges or shortcomings of this technique, namely the quality of the power produced is still decreasing. Several recent studies have explored to improve the quality of this power. Conventional PWM, but uses a triangular signal composed of the reference signal that has been assigned a Third Harmonic Injection (THI) which is called a decomposition signal.

To answer this challenge, this paper proposes a new scheme called Advance Carrier Based Pulse Modulation (ACBPWM) with decomposed modulation signal. This scheme does not use a triangular carrier waveform in the same amplitude as in conventional PWM, but uses a triangular signal composed of the reference signal that has been assigned a Third Harmonic Injection (THI) which is called a decomposition signal.

## 2 Sinusoidal Decomposition

#### 2.1 SPWM (Sinus Pulse Width Modulation)

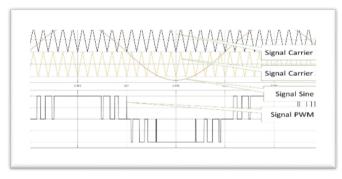

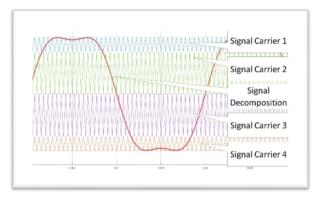

To generate a sinusoidal PWM signal, a sine wave is provided as the reference signal. The frequency of the sine wave is equal to the frequency of the desired output voltage with respect to the modulation of the carrier signal. The frequency of the carrier signal must be higher than the frequency of the reference signal. When both signals are modulated, it will generate a signal pulse for the switching device for the inverter as shown in Fig. 1 Table 1.

Fig. 1. Sinusoidal Pulse Width Modulation (SPWM).

To generate these signals, Eq. (1) is used, likewise for harmonic signals. This signal will be used as a reference signal or modulation signal in the CBPWM.

$$V_m m\{\sin(\omega_o t) + k.\sin(3.\omega_o t)$$

(1)

With  $V_m$  = Amplitude,  $\omega_o$  = frequency, t = time, m = Modulation index, k = Orde harmonic.

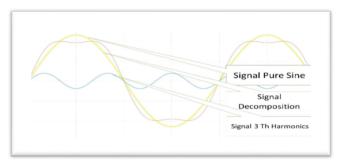

#### 2.2 Third Harmonic Injection Method

By injecting the third harmonic signal into a sinusoidal signal, we will get a decomposed modulation signal as shown in Fig. 2.

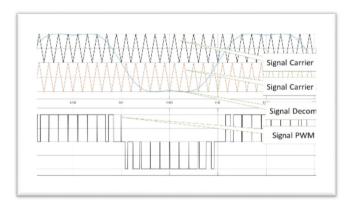

The reference or modulation signal is a third harmonic injection signal which will be modulated with a carrier signal as shown in Fig. 3. After being modulated, this signal will generate a signal in the form of a pulse which can then be used as a switching device in the inverter. Signal switching as shown in Fig. 3.

Fig. 2. Decomposition with Third Harmonic.

Fig. 3. Decomposition signal with two signals.

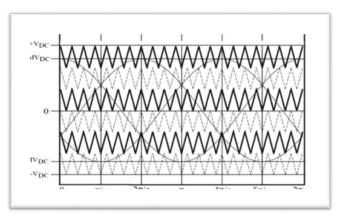

Fig. 4. CBPWM 7 level.

### 3 Advance Carrier Based Pulse Width Modulation

The carrier signal with a triangular shape will serve to get the trigger signal. The proposed method applies a simple logic: If the carrier wave is greater than or equal to the modulating wave the value is high and the switch is turned on and vice versa. Mathematically it can be written as follows:

$$if C_r \ge C_m then On$$

$$C_r \le C_m then Off$$

(2)

The general idea for CBPWM is to use multiple triangular carrier signals, with one carrier signal for each level. For the modulating signal (reference). A carrier signal can be used to signal each phase. If the CBPWM is applied for N phases, reference signal (modulation) corresponds to the number of phases. Figure 4 shows the modified reference signal and carrier signal with a phase shifted while the level is kept constant. The levels of the positive and negative sides are the same so that this CBPWM produces an inverter level 7 CBPWM.

### 4 Proposed Scheme

#### 4.1 Decomposition of Signals

The scheme proposed in this paper is shown in Fig. 5. Each carrier wave in CBPWM has voltage amplitude a peak-to-peak (vpp) equal to that of each source DC voltage. In this figure, the peak-to-peak voltage (vpp) of the carrier wave 3 is -0.75 Vdc and the carrier signal 1 is 0.75 vpp while the carrier signal 2 is 0.25 Vdc and the negative of the carrier signal 4 is -25 Vdc, the vpp of the decomposition modulation signal is equal to VDC. Figure 5 shows the implementation of the proposed scheme is similar to the conventional CBPWM modulation technique, the difference is that the carrier signal shifted two up the positive axis and two down the negative axis. The signal amplitudes have the same magnitude, i.e. each other has the opposite value.

61

Fig. 5. Composition of new carrier wave.

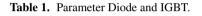

| DIODE                    | IGBT              |

|--------------------------|-------------------|

| C1=C2=4.7e-3 F           | Ron= 0.001 Ω      |

| R1=R2 0.01Ω              | $Rs = 1e5 \Omega$ |

| R Snubber = 250e-9F      | Cs = inf          |

| Ron=0.001 Ω              | Speed Time=5e6 s  |

| R Snubber = 500 $\Omega$ | Vdc=100 Volt -    |

| Vf= 0.8 Volt             |                   |

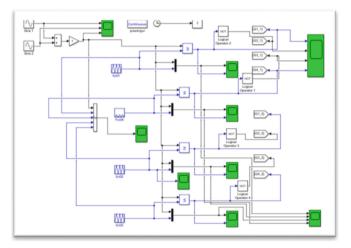

Fig. 6. Block Diagram of ACBPWM.

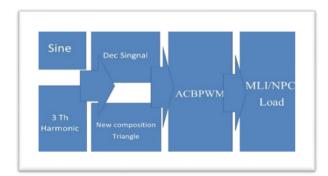

#### 4.2 Block Diagram of Advanced Carrier Based Pulse Width Modulation

The first carrier wave with a value of 0.75 Vdc, the second carrier wave of 0.25 Vdc which is lowered to the level above, as well as for the negative side. The basic concept

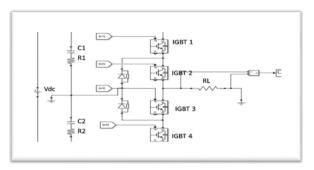

Fig. 7. The Scheme of NPC With Resistive Load.

Fig. 8. Scheme Detail for ACBPWM.

proposed this time is to use a Neutral Point Clamped multilevel inverter load. It looks like Fig. 6. The parameters of the NPC inverter are shown in Table 1.

The block diagram of the ACBPWM control scheme is shown in Fig. 6. The sine signal is injected with the third harmonic signal to produce a decomposition signal. The decomposition signal is compared with the new triangular pattern signal (New Composition) into ACBPWM which is then used to control the Multilevel Inverter, in this case the NPC. Figure 7 shows a single-phase NPC scheme using IBGT. The ACBPWM technique is shown in Fig. 8 which is equipped with a measuring instrument using MATLAB Simulink software.

#### 5 Result and Discussion

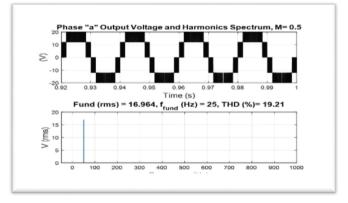

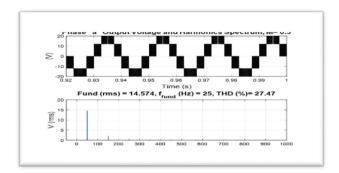

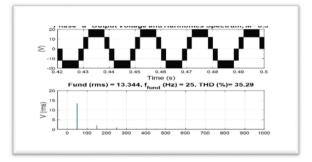

The results of the simulation of the proposed scheme are shown in Figs. 8, 9, 10, and 11. Figure 9 shows the conventional CBPWM modulation technique. In this method the carrier signal has the same amplitude in the positive and negative cycles. The complete

|    | Result Test Modulation Technique |       |        |        |        |  |

|----|----------------------------------|-------|--------|--------|--------|--|

|    | Modu-                            | THD i |        | THD v  |        |  |

|    | lation                           |       |        |        |        |  |

| No | Index                            | CBPWM | ACBPWM | CBPWM  | ACBPWM |  |

| 1  | 0,10                             | 3,23  | 2,17   | 337,00 | 252,20 |  |

| 2  | 0,15                             | 2,05  | 2,29   | 272,50 | 198,80 |  |

| 3  | 0,20                             | 2,51  | 2,63   | 231,90 | 163,10 |  |

| 4  | 0,25                             | 13,40 | 9,93   | 203,30 | 139,30 |  |

| 5  | 0,30                             | 7,86  | 7,30   | 181,70 | 120,80 |  |

| 6  | 0,35                             | 7,42  | 6,48   | 161,80 | 105,00 |  |

| 7  | 0,40                             | 7,64  | 5,19   | 147,00 | 91,53  |  |

| 8  | 0,45                             | 7,96  | 6,71   | 134,00 | 79,88  |  |

| 9  | 0,50                             | 8,25  | 5,31   | 124,10 | 68,39  |  |

| 10 | 0,55                             | 8,52  | 5,68   | 116,00 | 57,92  |  |

| 11 | 0,60                             | 8,70  | 8,31   | 106,40 | 49,34  |  |

| 12 | 0,65                             | 8,59  | 6,34   | 97,94  | 45,97  |  |

| 13 | 0,70                             | 8,49  | 6,29   | 90,31  | 44,40  |  |

| 14 | 0,75                             | 8,29  | 8,07   | 83,22  | 43,23  |  |

| 15 | 0,80                             | 7,91  | 6,10   | 76,97  | 42,01  |  |

| 16 | 0,85                             | 7,61  | 6,55   | 70,94  | 40,73  |  |

| 17 | 0,90                             | 7,23  | 5,42   | 64,68  | 39,38  |  |

| 18 | 0,95                             | 6,73  | 6,15   | 58,37  | 37,12  |  |

| 19 | 1,00                             | 5,84  | 4,76   | 52,21  | 36,36  |  |

| 20 | 1,05                             | 5,52  | 5,21   | 46,47  | 31,67  |  |

| 21 | 1,10                             | 4,67  | 4,42   | 38,62  | 29,94  |  |

| 22 | 1,15                             | 4,10  | 3,90   | 32,73  | 27,12  |  |

Table 2. Comparison of results with motor loads.

Fig. 9. Voltage Output from Decomp CBPWM.

increase in the complete modulation index is shown in Table 2. Figures 9, 10 and 11 show a decrease in THD. This decrease gives an indication that this technique can improve the power quality of the inverter. The details can be shown in Table 2.

By setting the modulation index from 0.1 to 1.15, the decrease in THD is very noticeable as well as the increase in power quality.

Fig. 10. Signal Output from Advance CBPWM.

Fig. 11. Signal Output from CBPWM.

### 6 Conclusion

The control scheme of the Advanced CBPWM technique Multilevel Inverter which is applied by adjusting the position of the carrier signal in the form of a triangle signal and modifying the signal on the modulating signal with the third harmonic signal decomposition technique. The proposed scheme improves power quality, by using a fixed dc source. Changes in the mean THD of 19,21%, 27,5% and 35,28%. For Advance CBPWM, decomposition CBPWM, Conventional CBPWM respectively.

Acknowledgment. Acknowledgments to the University of Mataram, for its financial support, and the Power Electronics and Drives Research Group, for their cooperation.

### References

Ponnusamy, P., Sivaraman, P., Almakhles, D. J., Padmanaban, S., Leonowicz, Z., Alagu, M., Ali, J. S. M.: A New Multilevel Inverter Topology With Reduced Power Components for Domestic Solar PV Applications. IEEE Access, vol. 8, 187483–187497 (2020).

65

- 2. Wiryajati, I. K., Giriantari, I., Kumara, I., Jasa L.: Speed Control Strategy for Three Phase Induction Machine Fed Inverter Base on Carrier Base Pulse Width Modulation (CBPWM). Engineering and Emerging Technology 5(1), 14–18 (2020).

- Stonier, A. A., Murugesan, S., Samikannu, R., Venkatachary, S. K., Kumar, S. S., Arumugam, P.: Power Quality Improvement in Solar Fed Cascaded Multilevel Inverter With Output Voltage Regulation Techniques. IEEE Access, vol. 8, 178360–178371 (2020).

- Taghvaie, A., Haque, M. E., Saha, S., Mahmud, M. A.: A New Step-Up Switched-Capacitor Voltage Balancing Converter for NPC Multilevel Inverter-Based Solar PV System. SN Applied Sciences, vol. 8, 83940–83952 (2020).

- Dasari, M. S., Mani, V.: Simulation and analysis of three-phase parallel inverter using multicarrier PWM control schemes, IEEE Access, vol. 2, 958 (2021).

- Jayakumar, V., Chokkalingam, B., Munda, J. L.: A Comprehensive Review on Space Vector Modulation Techniques for Neutral Point Clamped Multi-Level Inverters. IEEE Access, vol. 9, 112104–112144 (2021).

- 7. Dhote, Y., Khambra, B.: Neutral Point Clamped Multi Level Inverter Based Unified Power Quality Conditioner. Research Volume, vol. 6 (2021).

- Shamouei-Milan, M., Hassanifar, M., Neyshabouri, Y., Golshannavaz, S., Nazarpour, D.: A New Hybrid T-type Nested Neutral Point Clamped (NNPC) Multilevel Inverter with Improved Voltage Balancing Strategy, in 2020 28th Iranian Conference on Electrical Engineering (ICEE), pp 1–6 (2020).

- 9. Lee, E., Kim, S., Lee, K.: Modified Phase-Shifted PWM Scheme for Reliability Improvement in Cascaded H-Bridge Multilevel Inverters. IEEE Access, vol. 8, 78130–78139 (2020).

- Guo, X., Wang, X., Wang, C., Lu, Z., Hua, C., Blaabjerg, F.: Improved Modulation Strategy for Singe-Phase Cascaded H-bridge Multilevel Inverter. IEEE Transactions on Power Electronics, 1 (2021).

- Sadoughi, M., Zakerian, A., Pourdadashnia, A., Farhadi-Kangarlu, M.: Selective Harmonic Elimination PWM for Cascaded H-bridge Multilevel Inverter with Wide Output Voltage Range Using PSO Algorithm,". in 2021 IEEE Texas Power and Energy Conference (TPEC), pp 1–6 (2021).

- Sundari, M. S.: Simulation of Cascaded H-Bridge Multilevel Inverter using OHSW PWM for the elimination of harmonics. Xi'an University of Architecture & Technology 13(1), 275–288 (2021).

- Radmanesh, H., and Kavoosi, A.: Novel Multilevel Inverter Switching Technique Based On Harmony Search Algorithm. in 2020 11th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), pp 1–6 (2020).

**Open Access** This chapter is licensed under the terms of the Creative Commons Attribution-NonCommercial 4.0 International License (http://creativecommons.org/licenses/by-nc/4.0/), which permits any noncommercial use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license and indicate if changes were made.

The images or other third party material in this chapter are included in the chapter's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the chapter's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder.