# The Design and Implementation of FPGA-Based Ultrasonic Obstacle Avoidance Car

Jun Yang School of Information Science and Engineering Yunnan University Kunming, China e-mail: junyang@ynu.edu.cn

Feng Zhang School of Information Science and Engineering Yunnan University Kunming, China e-mail: dingxiangwutong@163.com Chen Zhong School of Information Science and Engineering Yunnan University Kunming, China e-mail: 625672133@qq.com

Hong Liu School of Information Science and Engineering Yunnan University Kunming, China e-mail: 1014553422@qq.com

Abstract—Along with social progress and scientific development, there is increasing demand for smart devices. In this paper, the design of ultrasonic obstacle avoidance car can be widely used in intelligent household, intelligent robots and other sports-related equipment. This paper will use Verilog HDL language to implement combining FPGA chip with ultrasonic ranging module and control motor drive to achieve the car's automatic obstacle avoidance function. The car uses the maze left hand rule for automatic obstacle avoidance, enable it to adapt to the complex working environment.

Based on the FPGA chip's high reliability, good expansibility, easy to transplant and the precise ultrasonic measurement, obstacle avoidance car will has good market prospects because of its high degree of flexibility, accuracy, real-time.

Keywords- FPGA; Intelligent household; Verilog HDL Left hand rule; Ultrasonic

#### I. INTRODUCTION

Along with the rapid development of science and technology, ultrasonic ranging is widely applied in industry, agriculture, transportation, environment, safety protection, the energy measurement and other scientific fields. The performance indexes of ultrasonic ranging such as measuring precision, measuring distance and measuring reliability and so on, has a very important role to improve the control precision and reliability of the related application system, enhance production efficiency, and promote the development of science and technology<sup>[1]</sup>.

At present, the mainstream of ultrasonic obstacle avoidance car on the market mostly use 8 bit or 16 bit single chip microcomputer as main control chip<sup>[2]</sup> which is responsible for receiving the echo, and producing drive signals, and then controlling the car to avoid obstacle. Although the cost is low, the measurement precision of the

transit time and drive efficiency of ultrasonic transducer are both very limited. Compared with traditional SCM, FPGA as a kind of high density field programmable logic devices not only solves the lack of custom circuits, but overcomes the shortcomings of original programmable gate device that the gate circuits are limited. And FPGA has many features such as perfect efficiency, portable, easy to operate, good secrecy performance, subtle real-time performance, high integration <sup>[3]</sup>.

This system adopts FPGA as the main control chip which controls the driver module through the real-time distance measured by ultrasonic module, and then leads the car to avoid obstacle intelligently. This design employs the L298N motor driver module which makes the circuit work stable duo to its high stability of SMT process and high quality aluminum electrolytic capacitor.

#### II. PRINCIPLE

## A. Ultrasonic Ranging

Ultrasonic is a kind of high frequency sound waves whose frequency is above 20000hz, beyond the limits of human hearing. Ultrasonic is insensitive to color, light and electromagnetic field, and has a strong ability to adapt to analyte that is in a harsh environment, such as dark, dusty, smoky, strong electromagnetic interference. Therefore, ultrasound has been widely used in modern industry, especially in industrial ranging<sup>[4]</sup>.

The principle of ultrasonic ranging formula is :

$$S=CT/2$$

(1)

Where, C stands for the known speed of ultrasonic wave in the air. When the temperature change is extremely tiny, we regard that the sound velocity is constant; T stands for the time difference between ultrasonic wave emitting and receiving circuit; S stands for the distance between the

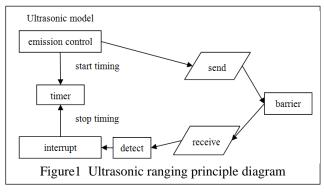

car and the barrier calculated by the previously mentioned formula. The schematic diagram is showed in Fig.1<sup>[5]</sup>.

### B. Maintaining the Integrity of the Specifications

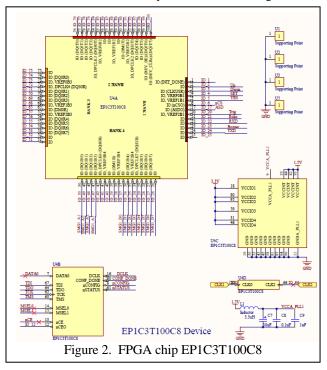

The core of ultrasonic ranging is to send and receive the ultrasonic signals. Traditional ultrasonic obstacle avoidance system mostly uses the single chip microcomputer as the main microprocessor. But there is fairly large time delay error when internal instruction running, its precision can't meet the requirements of precision measurement. This design introduces FPGA into the design of ultrasonic obstacle avoidance car because its high speed and rich on-chip resources <sup>[6] [7]</sup> can replace single chip microcomputer to enhance the control precision of the frequency of ultrasonic work and the measurement accuracy of ultrasonic transceiver transit time. FPGA produces ultrasonic drive signal and starts timing through the accurate control of clock. Then after being amplified by ultrasonic emission module , driving signal drives ultrasonic transducer to emit sound wave. FPGA detects the echo signal that is reflected by barrier and filtered and amplified by ultrasonic receiving module. Finally, displays output after calculating. This FPGA the chip EP1C3T100C8 used in the system is shown in Fig. 2.

#### C. Motor Drive

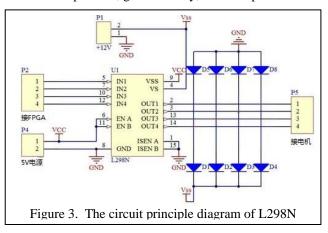

This system uses L298N as a motor driver chip. L298N is a full bridge drive chip with high voltage and large current. And its corresponding frequency is very high. L298N can drive 2 two phase or 1 four phase stepper motor at the same time, receive standard TTL logic level signal, and can directly regulate the output voltage through the power supply. This chip's simulative timing signals can be directly provided by FPGA's IO port. The circuit principle diagram of L298N is shown in Fig.3. Where, the ISENA and ISENB ports can connected to the current detection resistance to control the load circuit; Between the OUT1, OUT2 and OUT3, OUT4 can respectively connect to two stepper motors; From IN1 to IN4 can input control potential to control motor to go forward and reverse; And enable pins ENA and ENB controls motor stalling. Using this chip as a motor drive, it has the characteristics of convenient operation, good stability, fantastic performance.

The motor drives the car to avoid obstacle through combining with the ultrasonic ranging, FPGA's signal processing while adjusting PWM to change the voltage and current on both ends of the motor to achieve the function of controlling the car's speed. The method of L298N controlling drive motor is shown inTable1. This way to adjust the car's speed is superior in adjustment smooth, wide speed range, overload ability, and can withstand the shock load, frequently achieve quick start, brake and reverse.

| Enable | left  |   | right |   | left     | Right    | car's    |

|--------|-------|---|-------|---|----------|----------|----------|

| EN     | motor |   | motor |   | motor    | motor    | state    |

|        | Α     | Α | В     | В |          |          |          |

|        | 1     | 2 | 1     | 2 |          |          |          |

| PWM    | 0     | 0 | 0     | 0 | stop     | stop     | stop     |

| PWM    | 0     | 1 | 1     | 0 | prograde | reverse  | turn     |

|        |       |   |       |   |          |          | right    |

| PWM    | 1     | 0 | 0     | 1 | reverse  | prograde | turn     |

|        |       |   |       |   |          |          | left     |

| PWM    | 0     | 1 | 0     | 1 | prograde | prograde | foreward |

TABLE I. THE CONTROL PRINCIPLE OF L298N

#### D. Maze Left Hand Rule

The maze left hand rule is not just a rule, but also the mirrors and reflection of materialist world outlook. It is a way to solve people's problem. For those wall maze, as long as along the walls and subconsciously turn left when encounter bend corner, can people walk out of the maze after a certain time. In this paper, the way that the car turns left when encounters obstacles is in accordance with the left hand rule. It's just like to meet a dead end when both the front and the left of the car have obstacles, the car turns left twice, and realize the backward movement, so as to achieve automatic obstacle avoidance.

#### III. THE FPGA IMPLEMENTATION OF ULTRASONIC OBSTACLE AVOIDANCE CAR

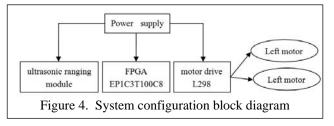

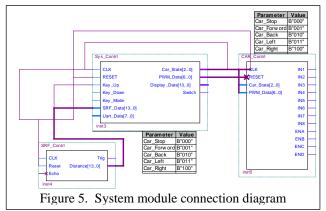

As shown in Fig.4, ultrasonic ranging module calculates the distance between the car and the barrier according to the formula S = CT / 2. When it equals warning distance, FPGA control s the motor driver module to make the car slow down; When it reaches the limit distance, FPGA controls the motor driver module to make the car turn left immediately according to left-hand rule; And when turns left twice, the car moves backward. This system with structured design, first completes the design of each module, and then integrates all modules together <sup>[8] [9]</sup> after correct simulation. The whole system consists of a ultrasonic ranging module, a microprocessor module and a motor driver module, the module connection is shown in Fig.5.

As shown in Fig.5, SRF\_Contrl is the ultrasonic ranging module, CLK is the processor clock input; Reset is the reset port; Trig is the control port terminal; IO port outputs high level at least 10 us, then the module automatically sends eight 40khz ultrasonic and detects if there is a return sound; Echo is receiving port; When there is return sound waves, gives the Echo port a high level , and the duration of the high level is the ultrasonic return time. Now the distance can be calculated by the data of Echo and Trig ports ,and can be output to FPGA through Distance port.

As shown in Fig.5, Sys\_Contrl is the microprocessor FPGA, it can receive real-time distance signal, and sends different signals to drive the car avoid obstacle and go forward. When the return distance of the ultrasonic ranging module is not greater than the preset alarm, FPGA will implement deceleration process; When the return distance, the car will turn left to avoid obstacle<sup>[9]</sup>.

As shown in Fig.5, the motor driver module CAR\_Contrl is the main executor of the obstacle avoidance function. The L298N motor driver module used in this system, can drive four motor at the same time. CLK is the system clock signal input; RESET is the reset signal input; CAR\_STATE is the car's control signal input; PWM\_DATA is the duty ratio signal input that used to control car's speed; IN1~IN8 is to control car's direction and stopping. ENA~END is to control the change of car's speed <sup>[10]</sup>.

The method of changing car's speed is to adjust the duty cycle PWM <sup>[11]</sup> to control the motor voltage and current. The duty ratio can be adjusted manually with ten rank from 10% to 100%. When duty ratio is 100%, the car will stop. When the car turns left, its left motor speed is zero, while the right side is not zero, and the default value is 50% duty cycle. The car's obstacle avoidance function can be realized under the synergy of three modules that the ultrasonic module provides distance measurement, the FPGA chip processes data and sends command, and the motor driver module executes command.

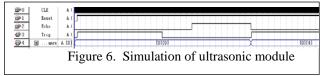

IV. THE SIMULATION OF ULTRASONIC OBSTACLE AVOIDANCE CAR

In the process of ultrasonic simulation module, it involves gathering real-time data of bluetooth module which cannot be achieved in the simulation environment. Therefore, we manually set data to simulate the returned data. As shown in Fig.5, when the reset signal is unsuccessful, the Trig port automatically sends a high level of more than 10us to stimulate the ultrasonic module to send ultrasonic waves. The ultrasonic module receives the returned ultrasonic waves after a period of time. The Echo port sends a high level and the Distance port displays the calculated distance to prepare for the next operation.

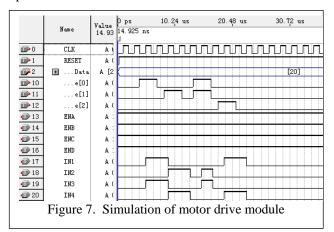

Fig.7 is the simulation diagram for the car drive control module. CLK is the clock signal input, RESET is the reset signal input, PWM\_Data is the duty ratio input, Car\_State is the car's state control input; ENA, ENB, ENC, END is the duty ratio output, and IN1, IN2, IN3 and IN4 stand for the motor drive output. In the simulation, the duty ratio is set to 20. The car's status is 0 means the four motor are no output; The status is 0, the car goes forward and the output is 1010; The status is 0, the car turns around and the output is 0101; The status is 3, the car turns left and the output is 0110; The status is 4, the car turns right and the output is 1001.

#### V. CONCLUSION

This paper introduces the detailed design process of ultrasonic obstacle avoidance based on FPGA. In the process of the hardware debugging of this system, the car can correctly realize the function of ultrasonic ranging, and FPGA can precisely control the motor driver module to realize the car movement and obstacle avoidance. The whole system with simple circuit structure, high precision of obstacle avoidance and fast runtime reduces the additional auxiliary components, and enhances the system's maintainability, portability and controllability. The system can be widely used in industrial control, radio and television, video surveillance, network security and automotive electronics and so on. It has a very good application prospect.

#### REFERENCES

- T.Schlegl, T. Bretterklieber, M. Neumayer and H. Zangl, "A Novel Sensor Fusion Concept for Distance Measurement in Automotive Applications," Graz University of Technology, Austria, 2010, pp. 755-778.

- [2] JingZhuo Shi, "Ultrasonic motor motion control theory and technology," Beijing: Science Press, 2011.

- [3] Wenxiang Zhang, Zhijn Li and Zihong Zhang, "SCM system design and development of the tutorial," Beijing: Electronic Industry Press, 2011.

- [4] Huihin Yang, "The design of the ultrasonic range finder," The Horizon of Science and Technology, 2012, 18 period.

- [5] Simon Monk, "Electronic DIY guides," Beijing: Posts and Telecom Press, 2014.

- [6] Hongtao li, Xiaohua zhu and Gu Chen, "Verilog HDL and the FPGA design and application development," Beijing: National Defence Industry Press, 2013, pp. 21-43.

- [7] Stephen Brown and Zvonko Vranesic, "Digital logic and Verilog design," Beijing: Tsinghua University Press, 2014.

- [8] Bin Yu, "Verilog HDL digital system design and simulation," Beijing: Electronic Industry Press, 2014.

- [9] Lingli Wang, Xuegong Zhou and Yin Wang, "System level the FPGA design and application," Beijing: Tsinghua University Press, 2012.

- [10] Wensheng Song and Xiaoyun Feng, "Traction power ac drive control and modulation technology," Beijing: Science Press, 2014.

- [11] (Japanese) Shidaosheng, "Small ac servo motor control circuit," Beijing: Science Press, 2013.