# Design of Airborne Strapdown Inertial Navigation System Based on DSP Structure

Jing YU 1, a, Hang GUO 2, b

aemail: 505896084@gg.com, bemail: guohang0001@126.com

**Keywords:** Airborne strapdown inertial navigation system, Digital signal processor, Micro inertial measurement group, Data acquisition

**Abstract.** An airborne strapdown inertial navigation system based on DSP is introduced. The TMS320F28335 and TMS320C6416 DSP chips of TI Company are used as the core components of the system, and the CPLD technique combined with the dual DSP structure of strapdown control and solution are used to realize logic circuit of the system. From the analysis of the hardware, software and overall design, the scheme can match the characteristics of the strapdown inertial navigation system, such as fast speed, high accuracy and good stability.

### Introduction

Inertial navigation system (INS) is an autonomous navigation system which developed at the beginning of the 20th century [1]. It depends on neither the external navigation station and information nor the spreading radio. INS has strong concealment and anti-jamming ability, which can provide real-time navigation parameters. The application of INS is divided into two types: mechanical platform inertial navigation system and strapdown inertial navigation system. Strapdown inertial navigation system does not need entity platform. The gyro and accelerometer are connected on the carrier directly. By the replace of inertial platform to computer, the INS is also referred to as mathematical platform. The main functions of mathematical platform are coordinate transform matrix and the attitude angle calculation [2]. The strapdown inertial navigation system has advantages such as simple structure, small size, light quality, low cost, fast initial alignment etc, and it has been widely used as the airborne navigation equipment [3].

Presently most strapdown inertial navigation systems adopt general computer core and architecture. However the general microprocessor of von Neumann structure has disadvantages such as slow data processing, large volume, high power consumption, complex circuit and low reliability, which is unable to meet the requirements of strapdown inertial navigation system on the miniaturization, high precision and real-time requirements [4]. The real-time information processing system based on digital signal processor (DSP) has the features as high-speed, stable, full digital. It has modified Harvard architecture, advanced multi bus and multi pipeline mechanism, dedicated hardware multiplier and efficient instruction set, and it is easy to be embedded in every kind of signal filtering and information integration algorithms with well real-time characteristic [5]. With the performance increase of DSP, the research and development of the DSP based airborne strapdown inertial navigation system has attracted many attentions [6].

## The overall structure of the system

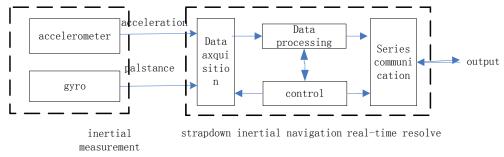

The strapdown inertial navigation system is composed of micro inertial measurement group, data acquisition and preprocessing unit, navigation solution unit and communication unit. The system structure is shown in Figure 1. The hardware circuit design and software design are introduced in this section.

<sup>&</sup>lt;sup>1</sup> Department of aeronautical armament engineering, The First aviation academy of Chinese air force, Xinyang, 464000, China

<sup>&</sup>lt;sup>2</sup> Department of aeronautical electronic engineering, The First aviation academy of Chinese air force, Xinyang, 464000, China

Fig.1. Strapdown inertial navigation system

In order to meet the control and reconciliation requirements of the strapdown system, we choose two superior DSP chips of TI company: TMS320F28335 and TMS320C6416 as the core of the system for control and operationrespectively.TMS320C6416 is mainly responsible for the algorithm realization and TMS320F28335 is responsible for the control of the input and output of the system. The combination of the two chips can achieve complementary advantages, and this can realize the strapdown control and solution system based on dual cores DSP [7].

## Hardware design

The hardware of strapdown inertial navigation sys-tem is composed of inertial sensing element, analog-to-digital conversion circuit, DSP circuit, two power supply circuits and so on. However, the calculation of the strapdown inertial navigation system is relatively large, and the processor should have a great data processing capability. The strapdown inertial navigation system will be faced with more disturb than the platform inertial navigation system, so the suppression of various interferences is considered in the design of the platform hardware, and the signal noise ratio (SNR) of the original signal is improved from the hardware aspect [8].

The whole circuit is divided into three modules: data acquisition module, computer module and control interface module. Data acquisition module is responsible for collecting data from inertial device. Computer module is the core of the whole system which is responsible for all calculation and control, including processor DSP real time signal processing and inertial navigation algorithm. Control interface module is responsible for the control and communication of computer module. Three modules are connected by the bus. Because the actual working environment of the hardware platform must include the power supply system, this system uses one power supply module with various voltage to meet the power demand.

## Data acquisition module

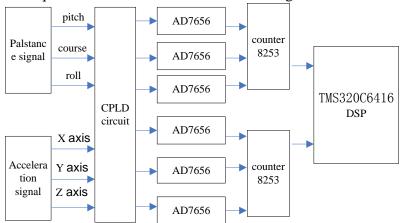

The data acquisition module can achieve the functions of the sensor output sampling, analog filtering, amplification, analog to data conversion. Inertial device is composed of three laser gyros and three accelerometers. The dynamic range requirement of the inertial measure device in strapdown system is very high. So three laser gyros signal by HCTL2020 are counted and then send to TMS320F28335, and the HCTL2020 control signals are controlled by CPLD through Schmitt trigger SN74ACI4.

TMS320F28335 is the latest DSP control chip, which has rich peripherals interface resources and powerful floating-point computing power. The main frequency of F28335 can up to 150MHz. It has a single precision floating-point unit (FPU). This chip has flexible GPIO configuration function with rich resources of control and communication interface, so it is very suitable for motor control and data acquisition as the core processing [9].

The output of accelerometer is the proportion of current signal, and the conversion is needed to obtain the data that the processor can accept. The V/F conversion has good anti-interference and high precision. Therefore, it is suitable for the analog to digital conversion. Accelerometer and odometer signals are counted by CPLD, and then the data are stored temporarily in register. The TMS320C6416 chip can read the data directly. The counter selects commonly used programmable time /counter 8253, which has three hex counters and each counter has independent input and output control register. The proposed system uses two 8253 to convert the pulse in six channels to

digital values at the same time, and then read by the TMS320C6416 chip.

The AD7656 is used as A/D conversion chip, which is high integrated degree and 6 channels sixteen bits successive approximation (SAR) ADC. It also has sixteen bits effective precision and 250k SPS high throughput rate per channel. There are an internal 2.5V reference voltage source and a reference buffer in the same package. The AD7656 also has high-speed parallel interface and serial interface, allowing the device to connect with a microprocessor (MCU) or a digital signal processor (DSP). Data acquisition module circuit is shown in Figure 2.

Fig.2. Circuit of data acquisition module

# Computer module

Computer module uses TI TMS320C6416 high-speed DSP as the central processing unit (CPU) in the system. The TMS320C6416 has 1 GHz clock frequency, and its primary characteristic is using the advanced very long instruction structure (VLIW), so it can implement eight instructions in each clock cycle and all the instructions can be conditional executed. At the same time, TMS320C6416 can finish 1024 bits fixed-point FFT in ten seconds, and this speed is faster than traditional DSP in one ore two orders of magnitude. The high-speed processing capability has irreplaceable advantages which can meet the system's real-time requirement.

## Control interface module

The control interface module mainly completes the communication between the CPU and the computer module, such as the output of navigation information, the input of the control signal, and the execution of the whole system. We use an UART chipTL16C752 to extend three asynchronous serial ports, and use high-speed USB chip CY7C68013 to extend a USB port and communicate with the external device. This control interface module controlled by CPLD, which is similar with the USB interface. The Control interface module principle block diagram is shown in Figure 3.

Fig.3. Control interface module.

## Software design

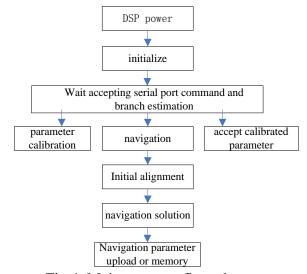

In the system the data processing and solution are mainly completed by the DSP. The software of TMS320F28335, TMS320C6416 is programmed by C and assembly language mixed programming method. The system exploitation is based on the SEED-XDA510USB development system as the hardware development platform, using CCS integrated debugging environment to complete the program debugging and hardware simulation. The main program flow chart is shown in Figure 4. TMS320F28335 module initialization program

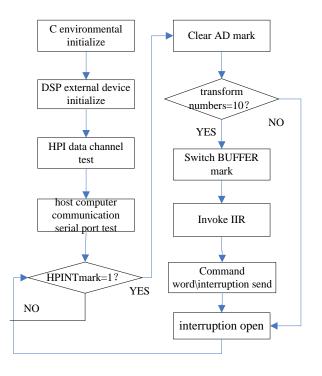

TMS320F28335 is the core of the control system, which is responsible for the channel calibration, channel switching, A/D acquisition and other control tasks. At the same time, it is the core of data preprocessing, using IIR low-pass filter in the data pre preprocessing, where the sampling rate is controlled by a DSP timer. The program flow chart is shown in Figure 5.

Fig.4. Main program flow chart

Fig.5. TMS320F28335 module initialization flow chart

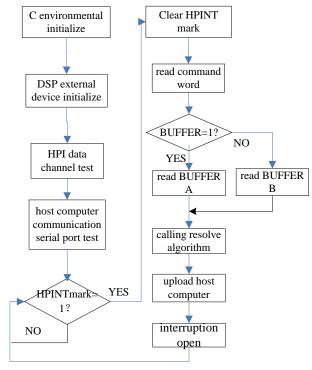

TMS320C6416 module initialization program

TMS320C6416 is the solution core of the system, and it is responsible for the solution of inertial navigation parameters, the ambiguity of the carrier phase integer ambiguity, and the Calman filter. The flow chart is shown in Figure 6.

# Conclusion

Through the analysis of the above system hardware circuit and the software, the proposed double DSP scheme can improve the computation accuracy and speed effectively in the strapdown solution system, which also can reduce the system volume, power consumption and cost. The logic circuits implemented by CPLD in the strapdown inertial navigation system are simple, high flexibility and reliability.

Fig.6. TMS320C6416 module initialization flow chart

### References

- [1] Zhang Lundong, Lian Junxiang, An improved compution scheme of strapdown inertial navigation system yusing rotation technique[J]. Journal of Central South University, Changsha, China, 2012(5): 25-32.

- [2] Huang Li, Approach of Improving the Inertial Navigation System Error for Large Transport Aircraft[J]. System simulation technology, Beijing, China, 2013: 123-129.

- [3] Godha S, Lachapelle G, Cannon M E. Integrated GPS/INS System for Pedestrian Navigation in a Signal Degraded Environment[C]//Proceedings of International Technical Meetings of the Satellite Division of the Institute of Navigation Forth, 2006: 2151--2164.

- [4] Morgado M, Oliveira P, Silvestre C. Design and experimental evaluation of an integrated USBL/INS system for AUVs[C]//Robotics and Automation (ICRA), 2010 IEEE International Conference, 2010:4264-4269.

- [5] Agarwal V, Arya H, Bhaktavatsala S. Design and Development of a Real-Time DSP and FPGA-Based Integrated GPS-INS System for Compact and Low Power Applications[J]. IEEE Transactions on Aerospace & Electronic Systems, 2009, 45(2): 443-454.

- [6] Miller I, Schimpf B, Campbell M, et al. Tightly-coupled GPS / INS system design for autonomous urban navigation[C]//Position, Location and Navigation Symposium on IEEE, 2008: 1297-1310.

- [7] Kim J, Ridley M, Sukkarieh S, et al. Real-time Experiment of Feature Tracking/Mapping using a low-cost Vision and GPS/INS System on an UAV platform[J]. Positioning, 2004, 3(1):167-172.

- [8] Li, Qian, Wang, Liduan, Zhai, Chuanrun, et al. Time synchronization design based on FPGA in integrated GPS/INS system[C]//Mechatronics and Automation, 2009. ICMA 2009. International Conference on IEEE, 2009: 3769-3774.

- [9] Wu X D, Wu S L, Wang J Q. A fast integrity algorithm for the ultra-tight coupled GPS/INS system[C]// ICSP 2008, 9th International Conference on IEEE, 2008: 583-2587.