# Variations in Hoop Stresses among Silicon Dioxide, Polystyrene and Polypropylene Carbonate Through Silicon Via Liners

Juma Mary Atieno<sup>1, a\*</sup>, Xuliang Zhang <sup>2,b</sup> and He Song Bai <sup>3,c</sup>

<sup>1,2,3</sup> University of Electronic Science and Technology of China, Room A1-406, Main Building, No.2006, Xiyuan Ave, West Hi-Tech Zone, 611731 Chengdu, China

<sup>a</sup>majuma84@yahoo.com, <sup>b</sup>majuma49@yahoo.com, <sup>c</sup>majuma.juma5@gmail.com

Keywords: Analysis System, Interconnect, Liner, Reliability, Through Silicon Via.

**Abstract.** Through Silicon Via are the widely used interconnects in the semiconductors industry. They are designed in different ways to meet the market demands. These interconnect need protection from both internal and external pressures. The pressures result from heating of the components on the chip which enhances expansion and contraction. Silicon dioxide has been the commonly used Through Silicon Via liner. We propose the use of polystyrene and polypropylene carbonate as liners to reduce overdependence on silicon dioxide. We compare deformations and stresses among the materials and noted that silicon dioxide had the least deformation and hoop stress values. We did further research and realized that the latter two materials have some good properties not found in silicon dioxide so they can also serve as better liners.

### Introduction

Reduction of feature sizes of transistors is a driving factor for performance improvement of chips over the last decade [1]. For many years now, the resistance-capacitance product of interconnects has been increasing due to scaling, while the RC product of transistors have improved with each technology node [2]. This difference has made interconnecting two points on a chip become very problematic with every new technology generation. Global interconnects were thought to be the most serious interconnect problem. This has clearly been discussed by researchers [3,4,5,6]. The resistance of interconnects become significant due to the dramatic increase in metal resistivity that emerge from size effects such as electron scatterings at the interconnect surfaces and grain boundaries, and also interconnect process variations [7,8,9,10,11].

### **Polymers** [12,13]

Polymers are chemically made from many repeating units. These repeating units are often made of carbon and hydrogen but sometimes; oxygen, nitrogen, sulfur, chlorine, fluorine, phosphorous, and silicon can be used. Polyethylene, polypropylene, polybutylene, polystyrene and polymethylpentene are examples of polymers that contain only carbon and hydrogen atoms. In our research we looked into polystyrene and polypropylene carbonate as materials used to design the Through Silicon Via liner. We compare their hoop stresses and deflection values to that of Silicon Dioxide which is a renowned TSV liner material.

### **Silicon Dioxide**

The growth of silicon dioxide is one of the most important processes in the fabrication of MOS transistors as discussed by some researchers [14]. Development of a reliable 3D integrated system is largely dependent on the choice of filler materials used in through-silicon vias. Several researchers [15,16,17] have preferred SWCNT and MWCNT bundles over Cu as prospective filler materials due to their higher conductivity.

## **Hollow Cylinders**

### **Internal Stresses**

Tangential stress is given by,

$$\sigma_{ti} = \sigma_t = \sigma_H = \frac{P_i(a^2 + b^2)}{(b^2 - a^2)}$$

(1)

Longitudinal stress is given by,

$$\sigma_l = \sigma_l = P_i^* \frac{a^2}{(b^2 - a^2)}$$

(2)

Radial stress;

$$\sigma_{ri} = \sigma_r = -P_i \tag{3}$$

### **External Stresses**

Tangential stress;

$$\sigma_{to} = \sigma_t = \frac{2P_i a^2}{(b^2 - a^2)}$$

Longitudinal stress:

(4)

$$\sigma_l = \sigma_l = P_i^* \frac{a^2}{(b^2 - a^2)} \tag{5}$$

Radial stress;

$$\sigma_{ro} = \sigma_r = 0 \tag{6}$$

Where,

$\sigma_H$  is the hoop stress,  $\sigma_l$  longitudinal stress and  $\sigma_r$  radial stress.  $P_i$  is the internal pressure experienced by the walls of the liners.

Each of the TSV liners with an internal radius of 5 micrometers, thickness of 2 micrometers and height 1 micrometer were subjected to a common internal pressure P<sub>i</sub>, of 1000 micropascals.

$$K = \frac{b}{a} \tag{7}$$

Where K is the ratio of external to internal radius. Substituting in equation 7, we have:  $K = \frac{b}{a} = \frac{7}{5} = 1.4$

Substituting the value of K in equation 1, the theoretical hoop stress is given by:

$1000\frac{1.4^2+1}{1.4^2-1} = 3083$  micro pascal

### Results

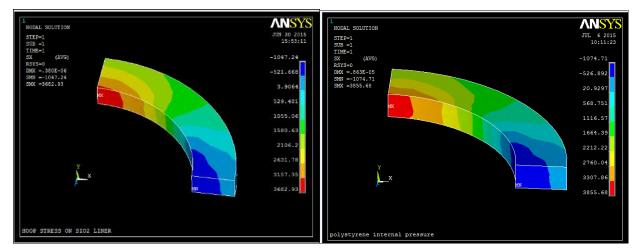

Fig. 1. Silicon Dioxide on the left and Polystyrene result on the right

| Table 1. Stresses summary |             |                                     |  |  |  |  |  |

|---------------------------|-------------|-------------------------------------|--|--|--|--|--|

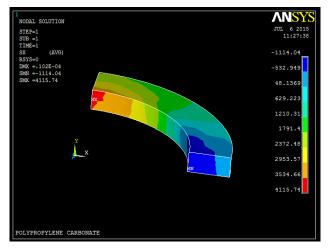

| Silicon Dioxide<br>(SiO₂) | Polystyrene | Polypropylene<br>Carbonate<br>(PPC) |  |  |  |  |  |

| -1047.24                  | -1074.71    | -1114.04                            |  |  |  |  |  |

| -521.668                  | -526.892    | -532.949                            |  |  |  |  |  |

| 3.9064                    | 20.9297     | 48.1369                             |  |  |  |  |  |

| 529.481                   | 568.751     | 629.223                             |  |  |  |  |  |

| 1055.06                   | 1116.57     | 1210.31                             |  |  |  |  |  |

| 1580.63                   | 1664.39     | 1791.4                              |  |  |  |  |  |

| 2106.20                   | 2212.22     | 2372.48                             |  |  |  |  |  |

| 2631.78                   | 2760.04     | 2953.57                             |  |  |  |  |  |

| 3157.35                   | 3307.86     | 3534.66                             |  |  |  |  |  |

| 3682.93                   | 3855.68     | 4115.74                             |  |  |  |  |  |

| Fig. | 2. | Pol | ypro | opylen | le car | bonate |

|------|----|-----|------|--------|--------|--------|

|------|----|-----|------|--------|--------|--------|

From the nodes more results were found. The theoretical stress applied on the materials was 1000 micropascal. The materials developed minimum stresses of between 1001 to 1007 which agrees with the theoretical value. The maximum stresses represent the hoop stresses. Silicon dioxide had the least hoop stress of 3055.5micropascal at node 144, while polypropylene carbonate had the highest hoop stress of 3098.6 micropascal at node 195. However, all the values comply with the theoretical one of 3083 micropascal but with minimum errors.

#### References

[1] J. D. Meindl, A. Naeemi, M. Bakir, and R. Murali. Nanoelectronics in retrospect, prospect and principle in Proc. IEEE ISSCC Tech. Dig., San Francisco, CA, Feb. 2010, pp. 31–35.

[2] M. T. Bohr. Interconnect scaling—The real limiter to high performance ULSI in Proc. Int. Electron Devices Meet., Washington, DC, Dec. 1995, pp. 241–244.

[3] R. Ho, K. W. Mai, and M. Horowitz. The future of wires. Proc. IEEE, vol. 89, no. 4, pp. 490–504, Apr. 2001.

[4] J. D. Meindl, R. Venkatesan, J. A. Davis, J. Joyner, A. Naeemi, P. Zarkesh-Ha, M. Bakir, T. Mule, P. A. Kohl, and K. P. Martin. Interconnecting device opportunities for gigascale integration (GSI) in IEDM ech. Di g., Washington, DC, Dec. 2001, pp. 23.1.1–23.1.4.

[5] J. D. Meindl, J. A. Davis, P. Zarkesh-Ha, C. S. Patel, K. P. Martin, and P. A. Kohl. Interconnect opportunities for gigascale integration. IBM J. Res. Develop., vol. 46, no. 2.3, pp. 245–263, Mar. 2002.

[6] J. A., R. Venkatesan, A. Kaloyeros, M. Beylansky, S. J. Souri, K. Banerjee, K. C. Saraswat, A. Rahman, R. Reif, and J. D. Meindl. Interconnect limits on gigascale integration (GSI) in the 21st century. Proc. IEEE, vol. 89, no. 3, pp. 305–324, Mar. 2001.

[7] S. M. Rossnagel and T. S. Kaun. Alteration of Cu conductivity in the size effect regime. J. Vac. Sci. Technol. B, Microelectron. Process. Phenom., vol. 22, no. 1, pp. 240–247, Jan. 2004.

[8] C. Durkan and M. E. Welland. Size effects in the electrical resistivity of polycrystalline nanowires. Phys. Rev. B, Condens. Matter, vol. 61, no. 20, pp. 14 215–14 218, May 2000.

[9] W. Steinhoegl, G. Schindler, G. Steinlesberger, M. Traving, and M. Engelhardt, Comprehensive study of the resistivity of copper wires with lateral dimensions of 100 nm and smaller. J. Appl. Phys., vol. 97, no. 2, pp. 023706-1-023706-7, Jan. 2005.

[10]G. Lopez. The impact of interconnect process variations and size effects for gigascale integration. Ph.D. dissertation, Dept. Elec. Comp. Eng., Georgia Inst. Technol., Atlanta, GA, 2009.

[11] J. Guillaumond, L. Arnaud, T. Mourier, M. Fayolle, O. Pesci, and G. Reimbold. Analysis of resistivity in nano-interconnect: Full range (4.2–300 K) temperature characterization. Proc. IEEE IITC, pp. 132–134, Jun.2003.

[12] F. F. C. Duval, C. Okoro, Y. Civale, P. Soussan, and E. Beyne. Polymer filling of silicon trenches for 3-D through silicon vias applications. IEEE Trans. Compon., Packag. Manufact. Technol., vol. 1, no. 6, pp. 825-832, 2011.

[13] C. Huang, Q. Chen, D. Wu, and Z. Wang. High aspect ratio and low capacitance through-silicon-vias (TSVs) with polymer insulation layers. Microelectron. Eng., vol. 104, pp. 12-17, Apr. 2013.

[14] J. D. Plummer, M. D. Deal, and P. B. Griffin. Silicon VLSI Technology - Fundamentals, Practice and Modeling. Prentice Hall Electronics and VLSI Series. Prentice-Hall Inc., Upper Saddle River, NJ, 2000.

[15] T. Xu, Z. Wang, J. Miao, X. Chen, and C. M. Tan. Aligned carbon nanotubes for through-wafer interconnects. Appl. Phys. Letts., vol. 91, no.4, pp. 042108-3, July 2007.

[16] C. Xu, H. Li, R. Suaya, and K. Banerjee. Compact AC modeling and performance analysis of through-silicon vias in 3-D ICs. IEEE Trans.Electron Devices, vol. 57, no.12, pp. 3405-3417, Dec. 2010.

[17] S. Kannan, A. Gupta, B. C. Kim, F. Mohammed, and B. Ahn. Analysis of carbon nanotube based through silicon vias," in Proc. 60th IEEE Int. Conf. Electronic Components Technology (ECTC), FL, pp. 51-57, 2010.