# An Ultra-low-power Integrated RF Front-end Based on Chip Transformer for UWB system

## Yi Li, Chunhua Wang, Kui Fu

College of Information Science and Engineering, Hunan University, Changsha 410082, P.R.China

Email:wch1227164@hnu.edu.cn

Keywords: ultra-low-power, UWB, CMOS, transformer

**Abstract.** In this paper, an ultra-low-power integrated RF front-end for UWB system is proposed. It contains a single-ended low noise amplifier (LNA) and a double balanced mixer. The resistive shunt feedback topology is employed to achieve a good input impedance matching in the whole UWB band. The stacked common-source (CS) LNA is adopting current-reuse and forward body bias techniques to reduce working current and voltage considerably. A transformer network is employed between LNA and double balanced mixer, which not just helps to convert the single-ended signal to differential signal, but also makes a great contribution to save the power consumption of the front-end circuit. Fabricated in the TSMC 0.18-µm RF CMOS technology, the S11 of the front-end is below -10dB in 3.1~10.6GHz. It achieves a conversion gain of 18.3~20.5dB, the double sideband (DSB) NF of 4.3~6.1dB. The IIP3 are -3.8dBm at 4.5GH. It consumes 2.4mA from a 0.8V supply voltage and occupies an active area of only 0.86\*0.52 mm<sup>2</sup>.

## Introduction

Ultra-wideband (UWB) technology has attracted great interest in both academia and industry in recent years for short range and high speed wireless communication systems. Recent developments have resulted in the development of CMOS radio frequency integrated circuits (RFICs) for UWB receivers. The receivers' gain and noise characteristics are closely related to the system sensitivity and dynamic range. However, it usually requires considerable power to boost the transistor performance. Therefore, many UWB receivers were developed at the expense of power consumption [1-3]. LNA and mixer are critical blocks in a UWB receiver. LNA usually determines the system NF and gain. This paper will propose an integrated ultralow-power front-end circuit for UWB receivers.

There have been several reported implementations of low power RFICs in the last few years [4-11]. Although these circuits' power consumption aren't low enough for satisfying the target of ultra-low-power RFICs, the techniques adopted by these researches to lower power still have significance for ultra-low-power RFICs. For ultra-low-power design of single module circuit, the most efficient technological method of reducing power consumption is to reduce supply voltage or current. Therefore, many effective techniques are adopted to achieve the aim. For example, folded cascade structure has been used in reference [8] to reduce the supply voltage, but it induced more branch current. Reference [9] introduced the subthreshold technique, which make the transistor work in a weak inversion region and reduce the supply voltage down to 0.6V. However, the subthreshold technique induced gain and NF performances degradation [10]. Recently, current-reuse topology and forward body bias technique are used to lower power consumption for RFICs [4, 10-11]. However, few researchers concentrate on the design of ultra-low-power LNA for multi-standard receivers, especially for UWB systems.

In this work, the front-end circuit adopts a resistive shunt feedback topology and a parallel LC load to achieve wideband input impedance matching in 3.1~10.6GHz [12]. Furthermore, the LNA reduces its power consumption by incorporating the current-reuse with forward body bias

techniques. To realize the monolithic integration between single-balanced LNA and doublebalanced mixer, the on-chip transformer is introduced. It not only helps to convert the singleended signal to differential signal, but also makes a great contribution to save the power consumption of the front-end circuit. Finally, the proposed circuit achieves a good performance over the whole UWB band range from 3.1 to 10.6GHz while the power consumption is extremely low.

## **Circuit Implementation**

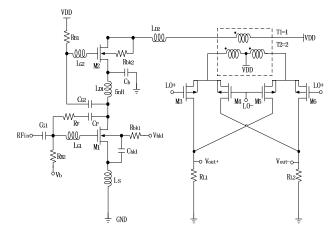

Fig. 1 Proposed ultra-low-power UWB receiver front-end circuit.

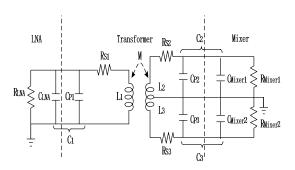

Fig. 3 The equivalent circuit based on transformer model.

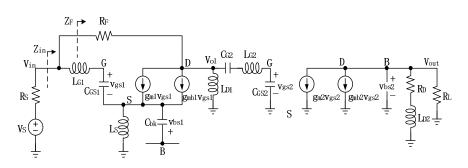

Fig. 2 Small-signal equivalent circuit of the LNA part.

The proposed integrated ultra-low-power RF front-end for 3.1~10.6GHz UWB system is shown in Fig. 1, the input stage was designed by employing a resistive shunt feedback topology together with a parallel LC load to match to a 50 $\Omega$  antenna. For flexibility of the design, a source degeneration inductor L<sub>S</sub> is placed in series with the source. The stacked structure of amplifying circuit is adopted to save more branch current. Moreover, current-reuse configuration is applied to the 2-stage cascade common source LNA. The signal amplified by M<sub>1</sub> is coupled to the gate of M<sub>2</sub> by C<sub>G2</sub> while the source of M<sub>2</sub> is bypassed by C<sub>b</sub>. Besides, forward body bias technique is applied to reduce the supply voltage of LNA. By adding a positive voltage V<sub>bk1</sub> and a current limiting resistor R<sub>bk1</sub> to body terminal of M1, forward body bias architecture of M1 is formed. The forward body bias voltage of M2 is directly obtained from the drain of M2, which helps to simplify the structure of bias circuit. With M1 and M2 sharing the same bias current and working at a low supply voltage, the power consumption of LNA is minimized. Moreover, the inductive load L<sub>D1</sub> and L<sub>D2</sub> of 1st and the 2nd amplifier stage help to achieve a high power gain, and the supply voltage won't be influenced since the voltage drop across them is negligible. A peaking inductor  $L_{G2}$  is added to the gate of M2 to double the 3dB bandwidth of the output stage, so the high frequency poles of the LNA can be pushed outside of the 3.1~10.6GHz band of interest.

To implement further low power design, an on-chip transformer is employed between LNA and mixer to convert the single-ended signal to differential signal, while it also provides current gain for the front-end circuit. The equivalent circuit based on transformer model is shown in Fig. 3. Where C<sub>P1</sub>, C<sub>P2</sub>, C<sub>P3</sub>, R<sub>S1</sub>, R<sub>S2</sub> are the parasitic parameters caused by on-chip transformer. R<sub>LNA</sub>, C<sub>LNA</sub> is the output impedance parameter of the LNA. R<sub>Mixer</sub>, C<sub>Mixer</sub> is the input impedance parameter of the mixer. Resonator  $L_1$ - $C_1$  is connected to the output of LNA, resonators  $L_2$ - $C_2$ and  $L_3$ - $C_3$  are connected to the mixer input using a center-tapped coil.

The current signal is transferred from  $L_1$ - $C_1$  to  $L_2$ - $C_2$  and  $L_3$ - $C_3$  through the magnetic coupling in the transformer. In this process, its contribution for saving power consumption as follows: First, it converts single-ended signal to differential signal without any power consumption, because the transformer consists of passive component. Usually, the traditional single to differential circuit consists of active transistors, which consume power. Second, the transformer directly injects current signal to the switching stage of mixer, which helps mixer save the power consumption of transconductance stage. Finally, the mixer become a single layer transistor structure while the transconductance stage it omitted, which make it work under a lower supply voltage and save more power. Therefore, the on-chip transformer make a momentous contribution for saving the power consumption.

#### **Input Matching**

The complete small signal equivalent circuit of the LNA part is shown in Fig. 2. Due to the forward body bias technique is applied to the NMOS transistors, the back-gate transconductance (gmb) of them shouldn't be ignored and it can be analyzed as followed:

$$g_{mb} = (\eta - 1)g_m \tag{1}$$

$$\eta = 1 + \frac{\gamma}{2\sqrt{2|\varphi_f| - V_{bs}}} \tag{2}$$

(2)

In the type g<sub>m</sub> is the transconductance of the NMOS transistor. V<sub>bs</sub> of the transistor increases, then  $\eta$  and  $g_{mb}$  increases, which has an influence on the following analysis. Considering the effect of the back-gate transconductance  $(g_{mb})$  caused by forward body bias technique, the input impedance is as Eq. (3):

$$Z_{in} = \left[ S(L_{g1} + L_S) + \frac{1}{SC_{gs1}} + \frac{(g_{m1} + g_{mb1})L_S}{C_{gs1}} \right] / Z_F$$

(3)

In the type g<sub>m1</sub> and g<sub>mb1</sub> are the transconductance and back-gate transconductance of M<sub>1</sub>, Z<sub>F</sub> is the impedance looking into the shunt resistive feedback, and can be given as:

$$Z_{F} = \frac{R_{F} + (SL_{L} / / \frac{1}{SC_{L}})}{1 + \frac{g_{m1} + g_{mb1}}{S^{2}C_{gs1}(L_{g1} + L_{S}) + S(g_{m1} + g_{mb1})L_{S} + 1} \bullet \left(SL_{L} / \frac{1}{SC_{L}}\right)}$$

(4)

The input matching bandwidth decreases with the increasing of R<sub>F</sub>, but the value of R<sub>F</sub> has an effect on the NF. There is a tradeoff between input matching bandwidth and NF when  $R_F$ =400 $\Omega$ , and other parameters used as follows: L<sub>G1</sub>=1.43nH, L<sub>S</sub>=0.1nH, C<sub>F</sub>=3.5pF, C<sub>G2</sub>=0.58pF, L<sub>G2</sub>=1.1nH, L<sub>D1</sub>=2.44nH, C<sub>b</sub>=3.3pF.

#### **Noise Analysis**

The noise figure of the first stage is critical to the whole circuit. The noise factor of the first stage is as follows:

. .

$$F \approx 1 + \frac{R_{G} + R_{LG1} + R_{SS} + R_{LS}}{R_{S}} + \frac{\delta \alpha \omega^{2} C_{gs1}^{2} R_{S}}{5(g_{m1} + g_{mb1})} + \frac{R_{F}[(L_{G1} + L_{S})C_{gs1}]^{2}}{R_{S}[(g_{m1} + g_{mb1})R_{F} - 1]^{2}} \bullet \left| S^{2} + S\left(\frac{\omega_{0,RF}}{Q_{RF}}\right) + \omega_{0,RF}^{2} \right|^{2} + \frac{\gamma(g_{m1} + g_{mb1})(R_{F} + R_{S})^{2} \bullet [(L_{G1} + L_{S})C_{gs1}]^{2}}{\alpha R_{S}[(g_{m1} + g_{mb1})R_{F} - 1]^{2}} \bullet \left| S^{2} + S\left(\frac{\omega_{0,D}}{Q_{D}}\right) + \omega_{0,D}^{2} \right|^{2}$$

$$(5)$$

In the type(5)

$$\omega_{0,RF} = \sqrt{\frac{1 + (g_{m1} + g_{mb1})R_s}{(L_{g1} + L_{S1})C_{gs1}}}$$

(6)

$$\omega_{0,D} = \frac{1}{\sqrt{(L_{G1} + L_S)C_{gs1}}}$$

(7)

$$Q_{RF} = \frac{C_{gs1}}{R_s C_{gs1} + (g_{m1} + g_{mb1})L_s} \sqrt{\frac{(1 + g_{m1} + g_{mb1})(L_{G1} + L_s)}{C_{gs1}}}$$

(8)

$$Q_{D} = \frac{C_{gs1}}{(R_{F} / R_{S})C_{gs1} + (g_{m1} + g_{mb1})L_{S}} \sqrt{\frac{L_{G1} + L_{S}}{C_{gs1}}}$$

(9)

In the type(5),  $R_G$ ,  $R_{SS}$  represent the thermal noise induced by gate and source resistors of M1.  $R_{LG1}$ ,  $R_{LS}$  are the thermal noise caused by  $L_{G1}$  and  $L_S$  while working at high frequencies. From Eq. (5), since NF=10log<sub>10</sub>F has been put in the form of a second order function of S, its frequency response is controlled by Q factors  $Q_{RF}$  and  $Q_D$ . However, from Eq. (8) and Eq. (9),  $Q_{RF}$  and  $Q_D$  is mainly impacted by the value of  $L_S$  and  $R_F$ , so we can decrease the NF by choosing suitable value of  $L_S$  and  $R_F$ .

#### **Gain Analysis**

The conversion gain of the front-end circuit is provided by the first stage, second stage of LNA and the transformer network. The body effects and parasitic capacitances are not considered. The voltage gain of the first stage of LNA can be expressed as Eq. (10):

$$A_{1} = \frac{V_{o1}}{V_{in}} = -\left(R_{F} / SL_{L} / \frac{1}{SC_{L}}\right) \cdot \left(g_{m1} - \frac{1}{R_{F}}\right)$$

(10)

$$g'_{m1} = \frac{g_{m1} + g_{mb1}}{S^2 C_{gs1} (L_{G1} + L_S) + S(g_{m1} + g_{mb1}) L_S + 1}$$

(11)

The voltage gain of the second stage of LNA is given by:

$$A_{2} = \frac{V_{out}}{V_{o1}} = -(g_{m2} + g_{mb2}) \left[ R_{B} / (R_{D} + SL_{D2}) \right] \bullet \frac{1}{S^{2}L_{G2}C_{gs2} + \left( 1 + \frac{C_{gs2}}{C_{G2}} \right)} \approx -(g_{m2} + g_{mb2}) \bullet (R_{D} + SL_{D2})$$

(12)

In the type  $g_{m2}$  and  $g_{mb2}$  are the transconductance and back-gate transconductance of  $M_2$ . The gain increases with the increasing of  $R_D$ , but too large  $R_D$  worsens output matching. Therefore,  $L_{D1}$  and  $L_{D2}$  are adopted to improve the gain at high frequencies. However, we can increase  $g_{m1}$  and  $g_{m2}$  to compensate the degradation of gain, but it will cause larger power consumption, so the tradeoff between gain and power should be considered. In this paper  $g_{m1}=24$ ms,  $g_{m2}=27$ ms.

The on-chip transformer provides a current gain by impedance transformation. The close form of the transformer network current gain can be derived as

$$i_{out} = \frac{-j2kQ\omega_n}{\left\{\omega_n \left[1 + jQ\left(\omega_n - \frac{1}{\omega_n}\right)\right]\right\}^2 + (kQ)^2} \bullet \frac{1}{2}\sqrt{\frac{R_s}{R_L}}$$

(13)

where

$$Q \equiv R_s C_1 \omega_o = R_L C_2 \omega_o \tag{14}$$

$$\omega_{o} = \frac{1}{\sqrt{L_{1}C_{1}(1-k^{2})}} = \frac{1}{\sqrt{L_{2}C_{2}(1-k^{2})}}$$

(15)

In the type k is the coupling coefficient, which is determined by the mutual inductance between the two coils of the on-chip transformer. In this design, an ideal transformer model has been employed to supply a current gain, and the coupling coefficient k=0.5.

### **Simulation Results**

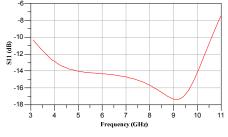

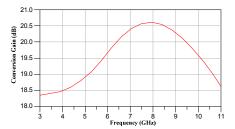

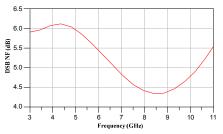

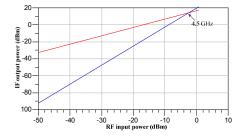

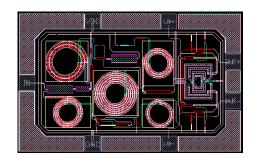

The RF receiver front-end is implemented in TSMC 0.18- $\mu$ m CMOS technology. The receivers' supply voltage falls to 0.8V when the forward body bias voltages are chosen at V<sub>bk1</sub>=0.44V. Operating in 3.1GHz~10.6GHz, the input reflection coefficient S<sub>11</sub> are respective less than -10dB which is shown in Fig. 4. The double sideband NF are 4.3~6.1dB as shown in Fig. 5. In Fig. 6, the conversion gain are 18.3~20.5dB. As shown in Fig. 7, the IIP3 of the front-end is -3.8dBm at 4.5GHz. The layout of the front-end is shown in Fig. 8, occupying 0.86\*0.52mm<sup>2</sup> active area. The power consumption is only 1.9mW, which is far below the same applied RFICs. Tab. 1 summarizes the performance of the proposed front-end and compares the recently reported UWB front-end. Our proposed front-end achieves an acceptable NF and linearity performances under ultra-low-power consumption.

Fig. 4 Simulation of  $S_{11}$  parameter of the front-end

Fig. 6 Simulation of conversion gain of the front-end

| Reference+2            | <b>[</b> 1] <i>•</i> | [2]+          | <b>[3]</b> ₽     | <b>[</b> 12]¢     | This Work+  |

|------------------------|----------------------|---------------|------------------|-------------------|-------------|

| BW (GHz)+3             | 3.1 ~<br>10.6₽       | 3~8.5+        | 3.1 ~<br>10.6+3  | 3.1 ~<br>10.6₽    | 3.1 ~ 10.64 |

| NF (dB)+               | 2.8 ~ 3.40           | 3.1 ~<br>4.4¢ | <b>4.5 ~ 5</b> ₽ | 3.74 ~<br>4.74ø   | 4.3~6.10    |

| S <sub>11</sub> (dB)43 | < -9.7₽              | < -11.50      | < -10.5₽         | < -8.6₽           | < -10+2     |

| Gain (dB)₽             | 11.0 ~<br>11.8+2     | 16.00         | 14.50            | 11.63 ~<br>12.89¢ | 18.3~20.5+  |

| IIP3 (dBm)+            | 0.72+3               | -5.40         | -4.8₽            | -40               | -3.80       |

| Supply (V)+            | 1.90                 | 1.247         | 10               | 1.80              | 0.80        |

| Power<br>(mW)+2        | 22.7+2               | 16₽           | 70               | 10.340            | 1.90        |

| Technology+            | 0.18µm₽              | 90nm≁         | 0.18µm₽          | 0.13µm₽           | 0.18µm₽     |

Tab. 1: Performance Summary of The Recently Reported UWB Front-end

Fig. 5 Simulation of double sideband NF of the front-end

Fig. 7 Simulation of the IIP3 of the front-end

Fig. 8 Layout of the RF receiver front-end

## Conclusion

This paper describes the design of an ultra-low-power RF front-end for UWB system. By employing transformer network and other power optimizing techniques, the total measured conversion gain of the receiver is 18.3~20.5dB and DSB NF is 4.3~6.1dB. The IIP3 are -3.8dBm at 4.5GHz. All of these results satisfy the requirements of the UWB receiver. Especially, the power consumption of the circuit is 1.9mW with a 0.8V supply voltage, which meets the demand for ultra-low-power applications.

## References

- [1] Lee, J. H., C. C. Chen, et al., 0.18μm 3.1-10.6 GHz CMOS UWB LNA with 11.4±0.4 dB gain and 100.7±17.4 ps group-delay. Electronics Letters, 2007. 43(24):p. 1359-1360.

- [2] Reja MM, Moez K, Filanovsky I, An area-efficient multistage 3.0 to 8.5GHz CMOS UWB LNA using tunable active inductors. IEEE Transactions on Circuits and Systems, 2010. 57(8):587-591.

- [3] Khurram M, Hasan SMR, Series peaked noise matched gm-boosted 3.1-10.6 GHz CG CMOS differential LNA for UWB WiMedia. Electronics Letters, 2011. 47(24):1346-1348.

- [4] Liu, J., H. Liao, and R. Huang, 0.5 V ultra-low power wideband LNA with forward body bias technique. Electronics Letters, 2009. 45(6): p. 289-290.

- [5] Tran, T.T.N., et al., Ultra-low-power series input resonance differential common gate LNA. Electronics Letters, 2011. 47(12): p. 703-704.

- [6] Dake, W., et al., A 0.4-V low noise amplifier using forward body bias technology for 5 GHz application. IEEE Microwave and Wireless Components Letters, 2007. 17(7): p. 543-545.

- [7] Shaeffer, D.K. and T.H. Lee, A 1.5-V, 1.5-GHz CMOS low noise amplifier. IEEE Journal of Solid-State Circuits, 1997. 32(5): p. 745-759.

- [8] Chih-Lung, H. and H. Yi-Lun. A low supply voltage dualband low noise amplifier design. in Consumer Electronics. IEEE 13th International Symposium on ISCE', 2009.

- [9] Chieh-Pin, C., et al., A high gain and low supply voltage LNA for the direct conversion application with 4-KV HBM ESD protection in 90-nm RF CMOS. IEEE Microwave and Wireless Components Letter, 2006. 16(11): p. 612-614.

- [10] Chieh-Pin, C., C. Ja-Hao, and W. Yeong-Her, A fully integrated 5 GHz low-voltage LNA using forward body bias Technology. IEEE Microwave and Wireless Components Letters, 2009. 19(3): p. 176-178.

- [11] Fu Kui, Guo Xiaorong, Wang Chunhua, Tu Yuxiang, Liu Chishi, McGeehan. Joe P. Low-power receiver serves multiple wireless Standards. Microwaves & RF, 2013. 52(2): 50-77

- [12] Yo-Sheng L, Chang-Zhi C, Hong-Yu Y, Chi-Chen C, Jen-How L, Guo-Wei H, Shey-Shi L, Analysis and design of a CMOS UWB LNA with Dual-RLC-Branch wideband input matching network. IEEE Transactions on Microwave Theory and Techniques, 2010. 58(2):287-296.

## **About Authors**

**Yi Li** He is currently studying in Hunan University for Ph.D. degree. His research interests include mobile communication network plan & optimization, RF design with focus on multi-mode receiver. E-mail: wch1227164@hnu.edu.cn