# Design of Mobile Phone Screen Display System Based on FPGA

Wei Dong Wang<sup>1, a</sup>, Jun Xian Wang<sup>2, b</sup> and Jing Wang<sup>3, c</sup>

<sup>1</sup>School of information, yunnan University, Kunming 650000, China;

<sup>a</sup>wwdynu@163.com

Keywords: FPGA, Mobile phone screen, Image display.

**Abstract.** In the current market, the mobile phone screen is often used for intelligent terminals, but it is very little used in the industrial and military applications are very few. In this paper, combining TKIS-I helmet color image sonar displayed on the phone screen project, we designed a FPGA-based phone screen display system, which can be achieved the display of high resolution images. This design which need only to modify the image display portion of the code can be applied to other areas to display various images. The design that is portability strong, speed and good reliability can be verified by experiment.

#### 1. Introduction

With the miniaturization of electronic product, the requirements are also getting higher and higher for monitor in industrial and military areas. Nowadays, the monitor that has a relatively high resolution with the VGA interface can meet the needs of the market, but the VGA interface monitor is relatively large in size. Therefore, the market appeared MIPI interface of monitor referred to as the mobile phone screen. In this paper, the system with a MIPI interface of monitor is designed, which is based on FPGA. The system is flexible and can be realized different images without changing the hardware.

## 2. System components and basic principles

#### 2.1 The basic components of the system

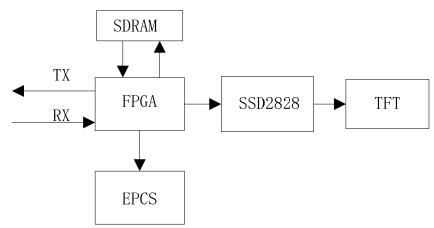

In this design uses Altera's Cyclone II EP2C5Q2C8C8N chip that does not support the MIPI interface of monitor. Therefore, between the FPGA and the cell phone screen plus a piece adapter plate to achieve VGA signal transduction MIPI signal. The overall structure of the design is shown in Fig.1.

## 2.2 The basic principle of the system displaying

We can see that the FPGA is able to receive a signal from an external signal, which is what we want to display on the mobile phone From Fig. 1. We can display the corresponding image on the mobile phone by the processing of the received data. The system is generally applied to the

acquisition of the signal to the corresponding processing on the mobile phone screen to display the image we need.

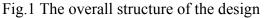

The mobile phone screen system is based on the differential signal display. Their phone screen interface is shown in Fig. 2. I can see TDN0, TDP0, TDN1, TDP1, TDN2, TDP2, TDN3, TDP3 are the differential signal between the four pairs of differential signal phase difference of 180 degrees in Fig. 2. Differential signal waveform diagram is shown in Fig. 3. We can see that D + and D- positive voltage between terminals represent a logic 1 from Fig. 3; Negative voltage represents the logic voltage between 0; no voltage means that the drive is in the tri-state which represents a high impedance state. In the case of the same interference source, two signals which with D+ and D- just offset form the same interference waveform, so you can achieve the common-mode interference. It can also enhance the signal amplitude (one positive and one negative, both of considerable magnitude in a line twice the amplitude). Therefore, high-definition images can be displayed on the phone screen..

Fig. 3 Differential signal waveform

#### 3. The design of the phone screen display system

Phone screen display system is composed of hardware and software.

#### 3.1 Hardware design

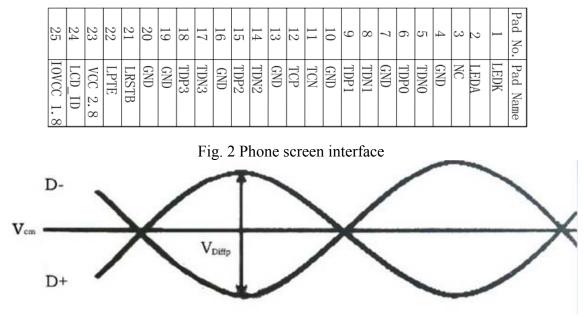

The hardware is based on the SOPC Builder FPGA. At the interface of the Builder SOPC call component, as shown in the following Fig. 3. From Fig. 3 we can see that the mobile phone display system based on FPGA is composed of CPU, SDRAM, JTAG, FPGA, LCD controller, UART and EPCS. The CPU is the heart of the system. The SDRAM is used for buffering data. The JTAG is mainly used to download programs. The LCD controller is used to provide timing and control for the mobile phone screen. The EPCS is used for the burning process. The UART is used for transmission of data.

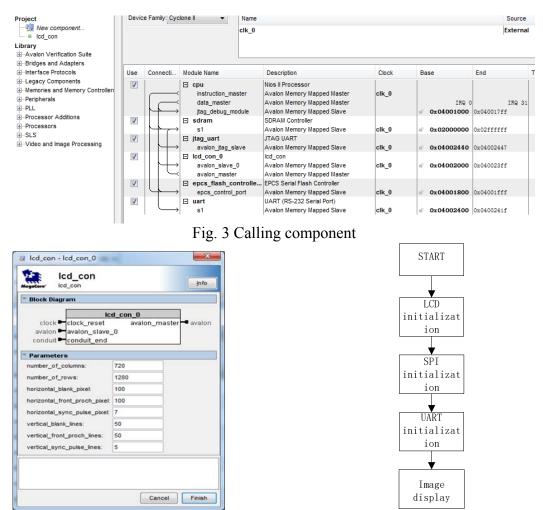

Fig. 4 LCD parameter setting interface **3.2 Software Design**

according to their phone screen resolution. The design interface is shown in Fig. 4.

Fig. 5 Software design process

#### 4. Experimental Verification

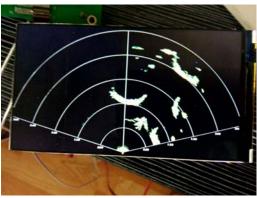

After the establishment of the mobile phone screen display system based on FPGA, the image display module is written in the code. We can use C language code in the NIOS II, so that the two-digit code can generate a set of 675 \* 176, and then use a two-dimensional linear interpolation algorithm to generate a two-dimensional array of 1280 \* 720, the two-dimensional array to fill to the corresponding pixel phone screen to get a fan as shown in Fig. 6. Fig. 7 is a transducer over the data collection process, receive data through the serial port to save the received data into an array, after a two-dimensional linear interpolation algorithm of sonar image. Through the experiment, the fan is proved to be fast and the image resolution is high.

Fig. 6 The sector of the two dimensional linear difference algorithm

Fig. 7 Sonar image obtained by fan

# 5. Summary

In summary, the FPGA based mobile phone screen display system is feasible and effective. The system can also be applied to other areas in the process of image display. We do not need to modify the configuration of the hardware, directly in the II NIOS system to write the code you need in the use of the process.

# References

[1] LiuTao, Xinghua Lou. Digital electronic system design and development examples navigation[M]. Beijing: People's Posts and Telecommunications Press, 2005:245 Reference to a book:

[2] Zhang Zhigang .FPGA and SOPC design Tutorial DE-2 practice [M] Xi'an: Xi'an University of Electronic Science and Technology Press, 2007: 138-144.

[3] Yi Feng. VGA controller for video conversion system design and implementation [J]. TV Technology Surgery. 2013.37 (23): 69-72.

[4] Guo Han Zhou. Monolithic SDRAM for data read and write operations pong design [J]. Changchun University of Technology technology, 2013,36 (5): 140- 143.

[5] Liao Yong Qing. Design and Implementation of Controller to display FPGA-based VGA image dynamic[J]. TV technology, 2011 (1 7): 52-54.