# Analytical Model of Channel Electric Field Profile in FinFET

Ming Fang<sup>1</sup>, Jin He<sup>1</sup>, Wen Wu<sup>1</sup>, Wei Zhao<sup>1</sup>, Ruonan Wang<sup>2</sup>, Mansun Chan<sup>1</sup>, Ping He<sup>3</sup> and Lei Song<sup>4</sup>

<sup>1</sup>Peking University Shenzhen SOC Key Laboratory, PKU Shenzhen Institute, China

<sup>2</sup>Shenzhen Huayue terascale chip Co., Ltd, Shenzhen 518097, P. R. China

<sup>3</sup>Shenzhen Emperor Electronic Technology Co., Ltd, Nanshan District, Shenzhen, 518108, China

<sup>4</sup>Shenzhen SuperD Co. Ltd, Huaqiaocheng, Nanshan District, Shenzhen 518053, China

Abstract—A simple analytical model for the lateral channel electric field profile in the velocity saturation region of the FinFET with undoped body is proposed and developed by solving the Poisson Equation in the velocity saturation region with a simplified boundary condition. The model has been verified with two-dimensional numerical device simulators and good agreement is obtained. Using the model, the impact of geometrical parameters including silicon film thickness, gate oxide thickness, and the terminal biases on the maximum lateral channel electric field in the FinFET can be predicted.

Keywords-double-gate MOSFET; FinFET; channel electrical field; velocity saturation

#### I. INTRODUCTION

As the scaling of bulk CMOS is approaching to the limit, double-gate (DG) MOSFETs such as FinFET have been considered to be the ultimately scalable CMOS technology due to their better immunity to short channel effect (SCE), better current drive and almost ideal subthreshold slope [1,2]. However, the hot-carrier effects such as the channel hot-carrier injection, impact ionization induced breakdown and device degradation pose other limits on the scaling of FinFET. To study the hot-carrier effects and their consequence, a channel electric field model, especially the maximum electric field at the end of the channel should be developed.

In this paper, an analytical channel electric field model based on a pseudo two-dimensional analysis in the velocity saturation region of FinFET with undoped body is proposed and developed. The model is extensively verified by a two-dimensional numerical device simulator MEDICI. The impact of scaling of physical parameters including silicon film thickness, gate oxide thickness, and channel length on the maximum channel electrical field is evaluated.

## II. MODEL

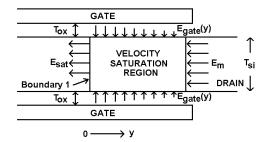

For the device operating in saturation regime, the channel of the Symmetric DG MOSFET, e.g. FinFET can be divided into gradual channel approximation (GCA) region and velocity saturation region (VSR). A schematic cross-section of the VSR of a FinFET with undoped body is shown in Figure 1. "Boundary 1" in the figure indicates the located in the channel where the velocity of carriers just saturates.

FIGURE I. A CROSS-SECTION OF THE SYMMETRICAL DG MOSFET WITH UNDOPED BODY. THE RECTANGULAR BOX ENCLOSED BY THE SOLID LINE IS THE VELOCITY SATURATION REGION WHERE GAUSS'S LAW IS APPLIED

The model is developed based on the pseudo two-dimensional approach proposed by Elmansy [3] and Ko [4]. Gauss's law is applied to the VSR (Figure 1)

$$\varepsilon_{si} \int_{\frac{Tsi}{2}}^{\frac{Tsi}{2}} E_{sat} dx - \varepsilon_{si} \int_{\frac{Tsi}{2}}^{\frac{Tsi}{2}} \frac{\partial V}{\partial y} \cdot dx - 2\varepsilon_{gate} \int_{0}^{y} E_{gate}(k) \cdot dk = -q \int_{\frac{Tsi}{2}}^{\frac{Tsi}{2}} \int_{0}^{y} Q(x,k) \cdot dk dx$$

(1)

where  $\varepsilon_{si}$  and  $\varepsilon_{gate}$  are the dielectric coefficient of silicon and gate insulator, respectively.  $T_{si}$  is the silicon film thickness, and Q is the mobile charge concentration per unit volume. To account for the non-uniformity distribution of the lateral electric field, it is assumed that the ratio of average lateral electric field to the surface lateral electric field in the VSR is independent of position y and is equal to the value at boundary 1 [3]

$$\int_{\frac{T_{si}}{2}}^{\frac{I_{si}}{2}} \frac{\partial V}{\partial y} \cdot dx = A \cdot T_{si} \cdot \frac{dV_{s}}{dy}$$

(2)

where  $V_s$  is the surface potential. The value of A at boundary 1 can be calculated using the vertical potential profile proposed by Yuan [5]

$$V(x) = -\frac{2kT}{q} \ln[\cos(B \cdot x)] + V_o$$

(3)

where  $V_o$  is the potential at the center of the silicon film and  $B = \sqrt{\frac{q^2 n_i}{2\varepsilon_{v}kT}} \cdot e^{\frac{qV_o}{2kT}}$ . For simplicity, the potential profile is

approximated by a parabolic function with a fitting parameter K

$$V(x) \approx K \cdot x^2 + V_o \tag{4}$$

Since the parameter K will be eliminated in the calculation of A, the exact value of K is not shown in the following calculations. The value of A is calculated by substituting (4) into (2)

$$A = \frac{1}{3} + \frac{2}{3} \cdot \frac{\partial V_o}{\partial V_s} \tag{5}$$

The partial derivative in (5) is calculated using equation (3)

$$A = \frac{1}{3} + \frac{2}{3\left(1 + \frac{B \cdot T_{si}}{2} \cdot \tan\left(\frac{B \cdot T_{si}}{2}\right)\right)}$$

(6)

Substituting (2) into (1) and differentiating both sides with respect to y, we get

$$\varepsilon_{si} \cdot A \cdot T_{si} \cdot \frac{d^2 V_s}{dy^2} = q \int_{\frac{T_{si}}{2}}^{\frac{T_{si}}{2}} Q(x, y) dx - 2\varepsilon_{gate} \cdot E_{gate}(y)$$

(7)

The integrated mobile charge term in (7) can be replaced by the gate electric field at boundary 1 with the assumption that GCA still holds at that location. Equation (7) becomes

$$\varepsilon_{si} \cdot A \cdot T_{si} \cdot \frac{d^2 V_s}{dv^2} = 2\varepsilon_{gate} \cdot \left[ E_{gate}(0) - E_{gate}(y) \right]$$

(8)

Since the gate electric field can be expressed as  $E_{gate}(y) = \frac{V_g - V_{FB} - V_s(y)}{T_{gate}}$ , where  $V_g$  and  $V_{FB}$  is the

gate and flat band voltage, respectively.  $T_{gate}$  is the gate insulator thickness. Equation (8) is rewritten to

$$\frac{d^2V_s}{dy^2} = \frac{\left[V_s(y) - V_s(0)\right]}{\lambda^2} \tag{9a}$$

and

$$\lambda = \sqrt{\frac{A \cdot \mathcal{E}_{si}}{2\mathcal{E}_{gate}}} \cdot (T_{si})^{\frac{1}{m}} \cdot (T_{gate})^{\frac{1}{n}}$$

(9b)

with m = n = 2. Using the boundary condition  $V_s(0) = V_{dsat}$

and  $\frac{dV_s(y)}{dy}\big|_{y=0} = E_{sat}$  at boundary 1, the solution of equation (9a) is given by

$$E(y) = E_{sat} \cdot \cosh(\frac{y}{\lambda}) \tag{10}$$

and

$$V(y) = V_{dsat} + \lambda \cdot E_{sat} \cdot \sinh(\frac{y}{\lambda})$$

(11)

It can be shown that the maximum lateral electric field  $(E_{m})$  at the end of the channel is

$$E_{m} = \sqrt{\frac{(V_{d} - V_{dsat})^{2}}{\lambda^{2}} + E_{sat}^{2}}$$

(12)

where  $V_d$  is voltage at the end of the channel.

#### III. RESULTS AND DISCUSSION

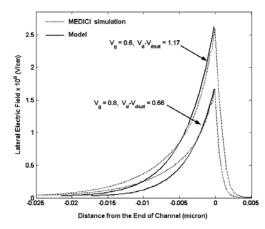

A 0.05 $\mu$ m SDG N-MOSFET with mid-gap work function gate-electrode and silicon dioxide gate insulator is used as a vehicle for the following simulations to evaluate the model. Extensive numerical simulations with MEDICI show that the parameter m in equation (9b) should be linearly from 2.03 to 1.97 as the  $T_{si}$  increasing from 5nm to 20nm. Figure 2 compares the results calculated from the model with the results obtained from MEDICI for the SDG device with  $T_{ox}$  =2nm,  $T_{si}$  = 10nm and  $E_{sat}$  = 3.5x10<sup>4</sup> V/cm [6]. Good agreement, is obtained between the model and the 2D simulation result especially near the peak E-field region where hot carrier effects is the most serious.

FIGURE II. COMPARISON OF THE RESULTS CALCULATED FROM THE MODEL WITH THE RESULTS OBTAINED FROM THE SIMULATIONS FOR THE SDG DEVICE WITH  $T_{ox}=2$ nm,  $T_{si}=10$ nm and  $E_{sat}=3.5$ x $10^4$  V/cm.

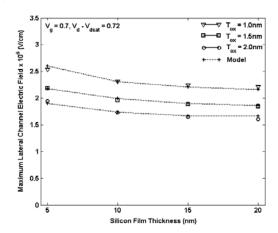

FIGURE III. THE PLOT OF THE MAXIMUM LATERAL CHANNEL ELECTRIC FIELD  $(E_m)$  AGAINST THE SILICON FILM THICKNESS  $(T_{si})$  AS A FUNCTION OF THE GATE OXIDE THICKNESS.

Figure 3 shows the maximum lateral channel electric field  $(E_m)$  versus the silicon film thickness  $(T_{si})$  with different gate oxide thickness  $(T_{ox})$  under the same biasing condition. The results from the model, again, show good agreement with the simulation results. As predicted by the model, the maximum electrical field increases with the reduction of  $T_{si}$  and  $T_{ox}$ . The impact of geometry scaling is included through  $\lambda$  which does not have an obvious scaling trend. However, there is a maximum value of  $\lambda$  which can be obtained by replacing the parameter A with its minimum value, giving

$$\lambda_{\max} = \sqrt{\frac{\varepsilon_{si}}{6\varepsilon_{gate}}} \cdot (T_{si})^{\frac{1}{m}} \cdot (T_{gate})^{\frac{1}{n}}$$

. This  $\lambda_{max}$  is an important

parameter to calculate the maximum  $E_m$  and evaluate the worst-case hot-carrier effects for a given SDG structure and biasing condition.

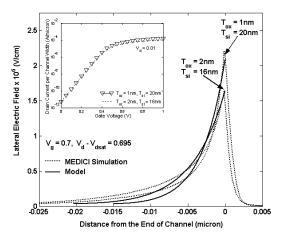

FIGURE IV. COMPARISONS OF THE LATERAL ELECTRIC FIELD FOR TWO SDG DEVICES WITH SAME OFF-STAGE CURRENT AND THRESHOLD VOLTAGE, BUT DIFFERENT PHYSICAL PARAMETERS SUCH AS  $T_{ox} = 1$ nm,  $T_{si} = 20$ nm and  $T_{ox} = 2$ nm,  $T_{si} = 16$ nm.

Figure 4 shows the lateral electric field for two SDG devices with same off-stage current and threshold voltage, but different  $T_{ox}$  and  $T_{si}$  with value shown in the figure. The  $I_d$ - $V_g$  characteristic of those SDG devices are shown as an insert in Figure 4. The results show that, those SDG devices have similar DC characteristic, but different  $E_m$ . Although scaling either the  $T_{si}$  or the  $T_{ox}$  can give us the same performance (e.g. off-stage current), the hot-carrier effects is more seriously affected by the scaling of  $T_{ox}$ . It also suggests that our proposed model can be used to study how different scaling approaches affect the hot-carrier effects.

## IV. CONCLUSION

We have presented a simple analytical model for the lateral channel electric field in the velocity saturation region of the FinFET with undoped body. This model compares well with the results obtained from the numerical two-dimensional simulator MEDICI. We also introduce an important parameter  $\lambda_{max}$  to characteristic the worst-case hot-carrier effects in a given FinFET structure and biasing condition. This model is simple and helpful to understand how the scaling of FinFET device affecting the hot-carrier effects.

#### ACKNOWLEDGMENTS

This work is funded by National Natural Science Foundation of China under Grants (61574005, 61306042, 61306045, 61306132, and 61274096). This work is also supported by the Fundamental Research Project of Shenzhen Science & Technology Foundation JCYJ 20140721163526514, and the International Collaboration Project of Shenzhen Science & Technology Foundation (GJHZ2015031615060422, SGLH20150213140604619).

# REFERENCES

- D. Frank, S. Laux, and M. Fischetti, "Monte Carlo simulation of a 30-nm dual-gate MOSFET: How far can silicon go?," *IEDM Tech. Dig.*, 1992, p. 553.

- [2] F. Balestra, S. Cristoloveanu, M. Benachir, J. Brini, and T. Elewa, "Double-gate silicon-on-insulator transistor with volume inversion: A new device with greatly enhanced performance," *IEEE Electron Device Letter*, Vol. 8, No. 9, pp. 410-412, 1987.

- [3] Y. A. El Mansy and A. R. Boothroyd, "A simple two-dimensional model for IGFET operation in the saturation region," *IEEE Transactions* on *Electron Devices*, Vol. 24, No. 3, pp. 254-262, 1977.

- [4] P. K. Ko, R. S. Muller and C. Hu, "A unified model for hot-electron currents in MOSFETs," *IEDM Tech. Dig.*, 1981, p. 600.

- [5] Y. Taur, "Analytic solutions of charge and capacitance in symmetric and asymmetric double-gate MOSFETs," *IEEE Transactions on Electron Devices*, Vol. 48, No. 12, pp. 2861-2869, 2001.

- [6] K. W. Terrill, C. Hu, P. K. Ko, "An Analytical Model for the Channel Electric Field in MOSFET's with Graded-Drain Structures," *IEEE Electron Device Letter*, Vol. 5, No. 11, pp.440-442, 1984