# A Constant current constant Voltage output mode of LED Drive

## ZhiJun Guo

Zhejiang University of Water Resources and Electric Power, Hangzhou, Zhejiang, China 310018

## 865418339@qq.com

**Keywords:** The LED driver, DC/DC converter, constant current + constant pressure

**Abstract.** In this paper, we design a LED driver, power factor correction circuit topology used + quasi resonant flyback type two level structure, the quasi resonant flyback type DC/DC transform part of the small signal model, design the system feedback loop parameters, to achieve the constant current drive + constant voltage output mode.

## Introduction

Energy and environment problem is becoming more and more serious, become a topic of common concern to people, energy saving and emission reduction in electricity consumption, the world about lighting electricity accounts for roughly 19% of the total generating capacity. Leds as energy saving, environmental protection, long service life new green light source, the LED lamps and lanterns to replace traditional lighting lamps and lanterns can save at least 40% of the energy consumption, in the current environment deterioration and energy shortage, LED lighting has a good space for development and broad market prospect.

LED belongs to low voltage driver cold light source, its performance the restriction of the drive power performance and thermal environment, the need of high efficiency and reliable special LED constant current drive power to match. For different power LED lamps and lanterns, driven by different topological circuit [1] [2] : 3 w to 20 w leds power scope, USES the primary side adjustment (PSR) flyback type topological structure, save the secondary feedback circuit, can achieve high efficiency, reduce cost, simplify the design and save PCB space; Within 20 w ~ 50 w a single-stage power factor correction (PFC) flyback type topological structure, within the limited space to achieve high power factor, and higher efficiency and reliability; Within 20 w ~ 100 w a power factor correction (PFC) + quasi resonant flyback type (QR) topology structure, with high efficiency, high reliability and low cost. According to different applications, different power is suitable for ball steep light, LED lamp, fluorescent lamp, plate lamp, industrial lamp, stage lamp, wall lamp, sign lights, street lighting and other applications.

## The working principle of the quasi resonant flyback type transformation

A. working principle

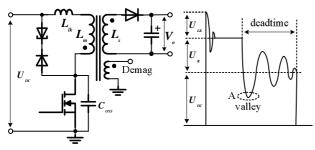

Quasi resonant flyback. the flyback converter with the traditional similar in form, as shown in figure 1. The difference is that quasi resonant flyback converter is much more than traditional flyback trough a certain voltage sequence detection circuit.

Transformer in the process of magnetic reset, due to the excitation inductance and stray capacitance on power tube, makes the switch tube voltage oscillation exists, as shown in figure 1, A point in the voltage oscillation curve, is the first minimum drain-source voltage switch tube (valley), if the MOSFET tube opening, the conduction current spike would be minimal, under certain conditions, even can achieve zero voltage switching (ZVS). No matter how much or line voltage when load is by adjusting the working frequency of change power supply, switch tube always stay at the bottom moment conduction. The flyback converter with discrete and continuous working mode, compared to reduce the loss of its opening, quasi resonant switch can improve efficiency and reduce the device temperature, reduce the electromagnetic interference.

### Figure 1 quasi resonant principle diagram B. transformer design

For quasi resonant mode, working frequency is changing, when the design, should work with the minimum frequency to determine the related parameters.

The flyback transformer output power:

he working principle of the quasi resonant flyback type transformationSection Headings.

$$P_o = \frac{1}{2} L_p I_p^2 f_s h \tag{1}$$

Through the flyback transformer primary winding is the maximum current:

$$I_{p(\max)} = \frac{V_{in}}{L_p} T_{on} = \frac{2 P_{in}}{V_{in(\min)} \frac{V_R}{V_{in(\min)} + V_R}}$$

(2)

The primary winding inductance value:

$$L_{p(\max)} = \frac{2 P_o}{I_p^2 f_{s(\min)} h}$$

(3)

When the design in order to use smaller size of the transformer, on the other hand in order to reduce switching loss and EMI noise, frequency values 50 khz to 100 khz. Converter, when the input voltage must be power increasing, the converter switching cycle; Reduce the output power and frequency increases, when the maximum power is still more than setting the power, the conduction time become smaller, into DCM work mode. Output power is constant, the input voltage is reduced, cycle of change increases, the minimum input voltage for the same power transmission, MOSFET turn-on time needs to change, when working under the lowest frequency. That is the inductance value is one of the biggest inductance value, if the inductance is too large, in order to obtain the same power to a lower frequency. In this article the values:  $f_{s(min)} = 60KHz$ ,  $V_{in(min)} = 220V$ ,  $V_R = 200V$ .

According to the formula (2) (3),  $L_p = 2mH$

#### The loop design

Design the driver of the excellent performance, after determine the topological structure and drive IC, loop parameters optimization calculation should also be considered. LED to constant current drive + constant voltage output mode, the voltage control loop and current loop contains two parts, the control loop changes the input voltage, load, constant voltage and constant current regulation and stability.

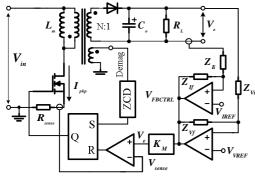

A. converter small signal model

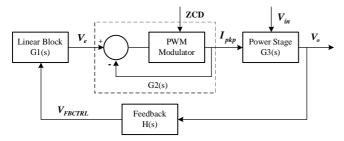

Drive at light load work in constant voltage mode, working principle is: the system output voltage is partial pressure sampling and reference voltage After the error amplifier is amplified by the linear change, as with the input of the comparator, while the current sampling signal from the switch tube as a comparator to the inverting input signal, when the phase of the signal amplitude exceeds the in-phase end, reset by RS flip-flop, through driving circuit shut off switch tube, make the original winding current is zero, the energy transferred to the deputy winding, current began to decline. When zero crossing detection circuit detected vice winding voltage to the bottom of resonance, by the RS flip-flop output a high level, and through the drive circuit open switch tube, the original winding current rise, its principle block diagram as shown in figure 2, the system loop structure diagram is shown in figure 3. Drive when overloaded work in constant current mode, principle of work. This design choose the control chip TEA1752 NXP.

Figure 2 quasi resonant flyback principle block diagram

Figure 3 system loop structure

Linear module transfer function  $G_1(s)$ :  $G_1(s) = \frac{\Delta V_e}{\Delta V_{FBCTRL}} = K_M, K_M = 0.66$  (4)

Contains the current loop PWM gain is simplified as:  $G_2(s) = \frac{\Delta I_{pkp}}{\Delta V_e} = \frac{1}{R_{sense}}$  (5)

Power level transfer function:

$$G_{VC}(s) = \frac{\Delta V_o}{\Delta I_{pkp}} = R_{sense} \frac{K_e}{-K_r + \frac{1}{R_I}} \frac{1 + \frac{s}{W_{zc}}}{1 + \frac{s}{W_{pl}}}$$

(6)

$$K_{r} = -\frac{V_{e} N^{2}}{2 R_{sense} V_{in}} \frac{1}{(1+N M)^{2}}, \quad M = \frac{V_{o} + V_{f}}{V_{in}}, \quad K_{e} = \frac{N}{2 R_{sense}} \frac{1}{1+N M},$$

Among them:  $W_{p1} = \frac{-K_{r} + \frac{1}{R_{L}}}{C_{o} (r_{c} (-K_{r} + \frac{1}{R_{L}}) + 1)}, \quad W_{zc} = \frac{1}{C_{o} r_{c}}$

Dc converter voltage control loop gain:  $A_{VC} = G_1(s) \ G_2(s) \ G_3(s) = K_M \ \frac{R_L \ N}{2 \ R_{sense}} \ \frac{h}{\frac{V_R}{V_{in}} + h + h \ \frac{V_R}{V_{in}}}$ (7)

Dc converter current control loop gain  $A_{ic}$ :  $A_{ic} = \frac{1}{R_L} A_{vc}$  (8)

#### **B** The feedback loop design

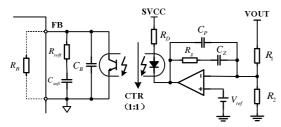

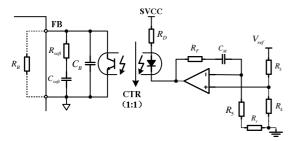

Feedback network has different structure, with the required tolerance and adjust the output voltage. In this paper, the voltage control loop feedback compensation adopts double pole of single zero compensation method, as shown in figure 4. Feedback compensation current control loop USES unipolar order zero compensation mode, as shown in figure 5. Use light coupling PC817 as primary and secondary electrical isolation, AP4310 double op-amp complete error with reference voltage signal amplification.

Voltage feedback network transfer function H(s):

Figure 4 voltage feedback control loop compensation circuit principle diagram

$$H_{v}(s) = \frac{\Delta V_{FBCTRL}}{\Delta V_{o}}$$

$$= R_{B} CTR \frac{1}{S R_{1} R_{D} C_{z}} \frac{1 + S R_{g} C_{z}}{(1 + S R_{g} C_{p})}$$

$$\frac{1 + S R_{soft} C_{soft}}{[1 + S (R_{soft} + R_{B}) C_{soft}] [1 + S (R_{B} C_{B})]}$$

Figure 5 current feedback control loop compensation circuit principle diagram

$$H_{I}(s) = \frac{\Delta I_{o}}{\Delta V_{FBCTRL}}$$

$$= R_{B} R_{S} CTR \frac{1+S}{S} \frac{R_{F} C_{M}}{R_{S} R_{D} C_{M}}$$

$$\frac{1+S}{\left[1+S\left(R_{soft}+R_{B}\right)C_{soft}\right]\left[1+S\left(R_{B} C_{B}\right)\right]}$$

Current feedback network transfer function  $H_{L}(s)$ :

#### Parameter design and the test results

By the above theoretical analysis, design the voltage control loop feedback compensation parameters are:  $R_1 = 51K$ ,  $R_2 = 4.1K$ ,  $C_p = 56pF$ ,  $C_z = 82nF$ ,  $R_g = 150K$ ,  $R_D = 5.1K$ ,  $R_{soft} = 39K$ ,  $C_{soft} = 330nF$ ,  $C_B = 10nF$ . Current control loop feedback compensation parameters is designed as follows:  $R_s = 0.1R$ ,  $R_3 = 100K$ ,  $R_4 = 5.04K$ ,  $R_5 = 150R$ ,  $C_M = 470nF$ ,  $R_F = 120K$ . Drive when the input voltage 220 v, the power factor is 0.975, the efficiency is 88.2%.

#### Acknowledgements

National high technology research and development program (863 program) project number 2014 AA052005

#### References

[1] Liu Yu, Jinming Yang, "The Topologies of White LED Lamps' Power Drivers," Power Electronics Systems and Applications, 2009. PESA.pp. 1-6, May. 2009

[2] Lianghui Xu, Hulong Zeng, Junming Zhang and Zhaoming Qian, "A primary side controlled WLED driver compatible with Triac dimmer," IEEE Applied Power Electronics Conf. (APEC). pp. 699–704, March. 2011.