# An Inductorless Variable-Gain Transimpedance Amplifier Design for 4GHz Optical Communication using 0.18-µm CMOS

Lee Bai Song Samuel<sup>1</sup>, Tan Yung Sern<sup>2</sup>, Thangarasu Bharatha Kumar<sup>1</sup>and Yeo Kiat Seng<sup>1</sup>

<sup>1</sup>Singapore University of Technology and Design, 8 Somapah Road, Singapore 487372 <sup>2</sup>Nanyang Technological University, 50 Nanyang Drive, Singapore 639798

**Keywords**: Automatic gain control circuit (AGC), Bandwidth enhancement, Optical receiver, Regulated cascode (RGC), Transimpedance amplifier (TIA), Variable gain feedback

**Abstract.** This paper presents a novel variable-gain inductorless transimpedance amplifier (TIA) design using Global Foundries 0.18- $\mu$ m CMOS technology which is suitable for high speed optical communication. A modified-RGC (M-RGC) preamplifier stage is used to reduce the input impedance through cascode and parallel PMOS transistor techniques for wideband operation. The amplifier stage uses common source amplifiers to increase the gain and an interleaving feedback technique to increase the bandwidth. The amplifier stage also has variable open-loop and resistive close-loop control mechanisms to vary the gain depending on the input signal strength without causing instability or a decrease in bandwidth. The proposed TIA has a transimpedance gain range of 45.4 dB $\Omega$  to 62.2 dB $\Omega$  for a dynamic range from0.2 $\mu$ A<sub>pp</sub> to 600  $\mu$ A<sub>pp</sub>. It has a bandwidth above 4.3 GHz throughout this range and a core dcpower consumption of 7.72 mW (total dc power with buffer is9.48 mW) for 1.8 V supply voltage.

#### Introduction

Due to the demand for faster data transmission speeds for optical communication, it is increasingly important to research on improving the different circuit blocks in the transmitter and receiver systems. The first circuit block in the receiver is the transimpedance amplifier (TIA), which determines many parameters such as the bandwidth, sensitivity and dynamic range of the entire receiver system[1] and thus is the most critical block in the system.

SONET OC-192 [1] is an important high-speed standard for digital communication. This is because it allows low-cost 850 nm wavelength vertical cavity surface emitting lasers (VCSEL) to be used to emit signals [2]. There are two pressing issues in TIA designs today. Firstly, a critical tradeoff occurs between the gain and bandwidth. Most researchers try to increase the transimpedance limit curve outwards with a high gain and high bandwidth in their designs[3]. The main cause of a limited bandwidth is due to the capacitive load from the photodiode, electrostatic discharge (ESD) protection and pads (grouped together as C<sub>pd</sub>) at the TIA input which lowers the dominant pole frequency andreduces the bandwidth. Thus this paper has come up with an effective way to isolate the input capacitance from affecting the bandwidth.

Secondly, there is a limited dynamic range for the input signal. Dynamic range refers to the ratio between the maximum to minimum input photocurrent suitable for the optical receiver [4]. A large dynamic range is desired because there is a large variation in received optical signal power [5] and to prevent saturation [4]. The lower limit is fixed by the sensitivity of the TIA, which is determined by the noise, while the upper

limit is determined by the distortion and nonlinearity of the large input signal usually because of the voltage headroom issue[4]. This paper solves the issue of the upper limit by devising an innovative variable gain design that is adaptive to the input signal strength. Thus when the input signal increases beyond a limit, the gain would proportionally decrease while maintaining the bandwidth.

This paper hasconsidered inductorless design techniques because on-chip spiral inductors require a larger area[2] and results in higher crosstalk that degrades performance [6].

## Regulated Cascode (RGC) TIA

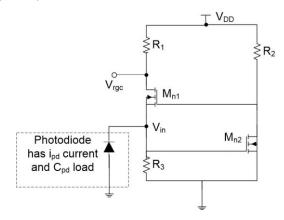

Figure 1.StandardRegulated Cascode (RGC) TIA

The RGC design shown in Figure 1 is common because of its low input impedance as compared to a conventional CG (common-gate) input stage [7]. The photodiode current signal goes into both the input of a CG and a CS (common-source) amplifier, with the CS output fed back to the gate of the CG transistor. This results in the input impedance lowered to  $1/g_{mn1}(1 + g_{mn2}R_2)$  instead of  $1/g_{mn1}$  for the CG itself. A lower input impedance of the RGC allows better isolation of the input capacitive load [6].

Transimpedance gain is calculated as [7]:

$$Z_T = \frac{V_{out}}{I_{in}} \approx \frac{R_1}{(1+s\omega_1)(1+s\omega_2)} \tag{1}$$

$$\omega_1 = \frac{c_{pd}}{g_{mn\,1}(1 + g_{mn\,2}R_2)} \tag{2}$$

$$\omega_2 = R_1(C_o + C_{amp}) \tag{3}$$

Where  $C_o \approx (1+g_{mn1}/g_{mn2})C_{gdn1}+C_{dbn1}$  and  $C_{amp}$  is capacitive load of the subsequent amplifier stage

The zero frequency transimpedance gain  $Z_T(0)$  and its input impedance  $Z_{in}(0)$  are calculated as [7]:

$$Z_T(0) \approx R_1 \tag{4}$$

$$Z_{in}(0) \approx \frac{1}{g_{mn \ 1}(1+g_{mn \ 2}R_2)}$$

(5)

For the 2 poles that are calculated, the pole in (2) is determined at the input node V<sub>in</sub>

For the 2 poles that are calculated, the pole in (2) is determined at the input node  $V_{in}$  and the pole in (3) is determined at the output node  $V_{rgc}$ . Although the input impedance is reduced, the input pole (2) is still the dominant pole due to the large capacitive load  $C_{pd}$ .

#### **Automatic Gain Control (AGC)**

An AGC circuit has an active and inactive mode. During the inactive mode, there is no change in the gain and bandwidth as input signal increases. However, in the active mode, the AGC circuit lowers the gain in an automatic and proportional manner. Hence this increases the dynamic range by raising the input signal upper limit [4]. This allows larger input signals into the TIA without being distorted by the voltage headroom issue at the last gain stage with the largest amplification.

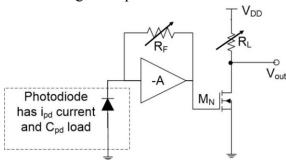

Figure 2.Example of the close-loop variable RF and open-loop variable RL

As shown in Figure 2, the 2 main methods of varying gain are to vary the close-loop resistor  $R_F$  or to vary the open-loop resistor  $R_L$ [5]. The variable resistors are created by transistors biased in the linear region with varying input gate voltages [9].

## Varying the Close-loop Resistor R<sub>F</sub>

$R_F$  refers to the feedback resistor across a negative gain stage and is a direct contributor of the gain of a shunt-shunt feedback TIA. If sufficiently large, the gain at zero frequency is equivalent to  $R_F[10]$ . When  $R_F$  is reduced, the amount of feedback current is increased and thus increases gain loss of the open-loop amplifier.

In an AGC circuit, as the input signal increases till the upper limit,  $R_F$  should be slowly reduced in order to reduce the gain. Hence  $R_F$  is implemented using a PMOS/NMOS transistor that has a varying  $V_{gs}$  that decreases/increases respectively.

#### Varying the Open-loop Resistor R<sub>L</sub>

$R_L$  refers to the load resistor of a common-source amplifier stage that contributes to the gain of that stage. The ideal gain of a common-source stage is taken to be  $-g_mR_L$ . Thus reducing the resistance directly reduces the gain of the stage. Both variable  $R_F$  and  $R_L$  are used in the design as they have complementary advantages explained later.

#### **Proposed TIA Preamplifer Stage Design**

The proposed RGC TIA preamplifier design is the same as that previously presented in [11].

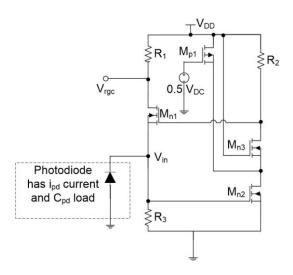

The RGC stage has 2 additional bandwidth-enhancing techniques that increase the isolation of  $C_{pd}$  from bandwidth determination, the first being a cascode transistor  $M_{n3}$  and second being a parallel PMOS  $M_{p1}toR_2$  and  $M_{n3}$  as shown in Figure 3.

Figure 3. Proposed modified RGC Preamplifier Stage

## Parallel PMOS M<sub>p1</sub> to R<sub>2</sub> and M<sub>n3</sub>

With an additional parallel PMOS M<sub>p1</sub>, the CS amplifier formed by M<sub>p1</sub> and M<sub>n2</sub> provides a greater transconductance  $g_{mn3}||(g_{mn2} + g_{mp1})|$  for the feedback transistor  $M_{n2}$ , henceloweringthe input impedance and isolating C<sub>pd</sub>. The dominant pole shifts from pole (2)to (3), hence increasing the bandwidth [12].

The input impedance of the preamplifier stage:

$$Z_{in}(0) \approx \frac{1}{g_{mn \ 1} \{1 + [g_{mn \ 3} || (g_{mn \ 2} + g_{mp \ 1})] R_2\}}$$

The bandwidth after addition of parallel PMOS:

$$f_{-3dB} \approx \frac{1}{2\pi} \times \frac{1}{R_1 \left( \left( 1 + \frac{g_{mn \, 1}}{g_{mn \, 2} + g_{mp \, 1}} \right) C_{gdn \, 1} + C_{dbn \, 1} + C_{amp} \right)}$$

(7)

Where C<sub>amp</sub> is the input capacitive load of the subsequent amplifier stage transistors  $C_{amp} = C_{gdCS1} + C_{gsCS1} + C_{gdRF1}$

## Cascode Transistor M<sub>n3</sub>

$C_{gdn1}$  and  $M_{n2}$ Miller effect in RGC also restricts the bandwidth as shown in (7). A cascode transistor M<sub>n3</sub> is added between the drain of the CS M<sub>n2</sub> and the gate of the CG  $M_{n1}$  and with a gate voltage of 0.5 V. This aidsin overcoming the Miller effect (1 + g<sub>mn1</sub>/(g<sub>mn2</sub> + g<sub>mp1</sub>)C<sub>gdn1</sub> and lowers the influence of C<sub>gdn1</sub> on the bandwidth of the dominant pole [13].

## Combined Gain and BW of Proposed TIA Preamplifier

Gain and bandwidth of Preamplifier Stage at V<sub>rgc</sub> from I<sub>in</sub>:

$$Z_{pre} = \frac{R_1}{(1+s\omega_{pre\ 1})(1+s\omega_{pre\ 2})} \tag{8}$$

$$\omega_{pre\,1} = \frac{c_{pd}}{g_{mn\,1}\{1 + [g_{mn\,3}||(g_{mn\,2} + g_{mp\,1})]R_2\}} \tag{9}$$

$$\omega_{pre\,2} = R_1(C_{gdn\,1} + C_{dbn\,1} + C_{amp}) \tag{10}$$

$$f_{-3dB} \approx \frac{1}{2\pi} \times \frac{1}{R_1(C_{gdn\ 1} + C_{dbn\ 1} + C_{amp\ })}$$

(11)

Although the bandwidth equation is similar to [13], this proposed design has better isolation due to  $M_{p1}$  that ensures that the dominant pole of the design follows (11) more closely than [13].

## **Proposed TIA Amplifier Stage Design**

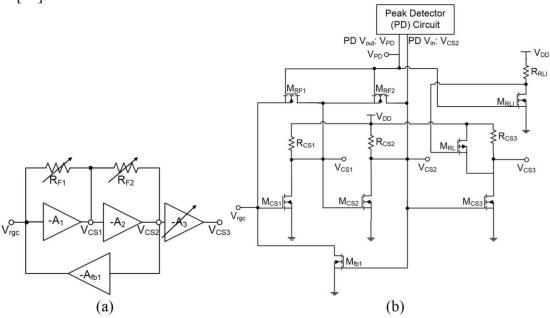

The proposed TIA amplifier design consists of 3 CS stages withan active interleaving feedback and an additional AGC function over that previously designed by the authors in [11].

Figure 4. (a) Simplified and (b) transistor-level Proposed Amplifier Stage

The amplifier stage is necessary in order to increase the gain from the RGC output since the signal is still too small for subsequent stages. The amplifier stage shown in Figure 4. There are 2 main innovative techniques in the amplifier stage. Firstly, an interleaving feedback transistor  $M_{\rm fb1}$  helps to increase the bandwidth. Secondly, there is an adaptive gain circuit using variable feedback resistors  $M_{\rm F1}$ ,  $M_{\rm F2}$  and  $M_{\rm L}$ .

There are several factors that contribute to poles in the amplifier stage. Firstly, each CS has a pole contributed by the load resistor and capacitance of the subsequent stage. Secondly,  $M_{\rm fb1}$  contributes to the pole of the combined first and second stages. Thirdly,  $M_{\rm F1}$ ,  $M_{\rm F2}$  and  $M_{\rm L}$  contributes to the poles of the first, second and third stages respectively. We calculated the contributed poles of the 2 innovation techniques separately and then combined them together.

#### Active Interleaving Feedback Transistor M<sub>fb1</sub>

The 1 CS feedback in between [14] which is  $M_{\rm fb1}$  creates an active feedback loop  $A_{\rm fb1}$ . An advantage of using active over passive feedback components is that there is less process variation during manufacturing [15]. Calculating the contribution of  $A_{\rm fb1}$  alone first, it generates a high frequency peaking caused by the introduction of a zero that helps increase the bandwidth and can be calculated as in [15]:

$$f_{Afb\,1, peak} = \frac{1}{2\pi} \times \frac{1}{R_{o,rgc}\,C_{o,rgc}} \tag{12}$$

Gainat  $V_{CS2}$  from  $V_{rgc}$  when accounting for only  $M_{fb1}$  could be estimated similar to [14]:

$$\frac{V_{CS2}}{V_{rgc}} = \frac{\left(\frac{A_1}{1 + s\omega_{amp 1}}\right)\left(\frac{A_2}{1 + s\omega_{amp 2}}\right)}{1 - \left(\frac{A_1}{1 + s\omega_{amp 1}}\right)\left(\frac{A_2}{1 + s\omega_{amp 2}}\right)\left(\frac{A_{fb1}}{1 + s\omega_{fb1}}\right)} = \frac{A_1A_2(1 + s\omega_{fb1})}{(1 + s\omega_{amp 1})(1 + s\omega_{amp 2})(1 + s\omega_{fb1}) - A_1A_2A_{fb1}} \tag{13}$$

$$\omega_{amp\,1} = \frac{1}{R_{d1}C_{o,CS\,1}} \tag{14}$$

$$\omega_{amp\,2} = \frac{1}{R_{d2}C_{o,CS\,2}} \tag{15}$$

$$\omega_{fb1} = \frac{1}{R_{o,rgc} C_{o,rgc}} \tag{16}$$

Where  $A_1$ =  $g_{mCS1}R_{CS1}$ ,  $A_2$  =  $g_{mCS2}R_{CS2}$  and  $A_{fb1}$  =  $g_{mfb1}R_{o,rgc}$  with  $R_{o,rgc}$  being the output resistance of the previous RGC stage into the first amplifier stage CS and where  $C_{o,CS1}$ = ( $C_{gdCS1} + C_{gsCS2} + C_{gsRF1} + C_{gdRF2}$ ),  $C_{o,CS2}$  = ( $C_{gdCS2} + C_{gsCS3} + C_{gdfb1} + C_{gsfb1} + C_{gsRF2} + C_{gdfb1} + C_{gsfb1}$ ) and  $C_{o,rgc}$  = ( $C_{gdRF1} + C_{gdCS1} + C_{gsCS1} + C_{gdfb1}$ ) which are defined as the load capacitances to  $V_{CS1}$ ,  $V_{CS2}$  and  $V_{rgc}$  respectively.

## AGC Variable Transistors $R_{F1}$ , $R_{F2}$ and $R_{L}$

A good AGC design would incorporate both varying  $R_F$  and  $R_L$  that would complement each other. A previous implementation in [5] controls both digitally. However, because it is a 6-bit binary control, it requires 6 parallel PMOS transistors in an array for varying both  $R_F$  and  $R_L$ , which increases chip area. In addition, this also requires an additional analog-to-digital converter (ADC) circuit.

The AGC circuit which is fully analog controlled contains 3 variable resistors  $R_{F1}$ ,  $R_{F2}$  and  $R_L$  that are controlled by the same input voltage  $V_{PD}$  from a peak detector circuit, which provides an increasing dc voltage from 1.2 V to 1.75 V as the small-signal current input from the photodiode increases from 0.2  $\mu A_{pp}$  to 600  $\mu A_{pp}$ , which is within the input current range from photodiodes [5].

$R_{F1}$  and  $R_{F2}$  are closed-loop NMOS variable resistors across the first CS and second CS stages respectively, while  $R_L$  is an open-loop PMOS variable load resistor of the third CS stage. NMOS resistors are used for  $R_{F1}$  and  $R_{F2}$  because of the output voltage of the peak detector that bias the gate, while an additional CS stage consisting of  $M_{RL1}$  and  $R_{RL1}$  flips the input signal to bias the PMOS  $R_L$ , which is preferred over NMOS due to the constant biasing source voltage of  $V_{DD}$ .

The gain and bandwidth of each node in the amplifier stage ( $V_{CS1}$ ,  $V_{CS2}$  and  $V_{CS3}$ ) can be calculated with the simplification of the active feedback loop  $A_{fb1}$  not taken into consideration.

Gain at  $V_{CS1}$  from  $V_{rgc}$ :

$$\frac{V_{CS1}}{V_{rgc}} = \frac{-A_1}{1 - A_1} \times \frac{1}{1 + s\omega_{amp \ 3}}$$

(17)

$$\omega_{amp\ 3} \approx \frac{(R_{CS1}||R_{F1}||R_{F2})C_{o,CS1}}{1 - A_1}$$

(18)

Where  $R_{F1}$ =  $r_{dsRF1}$  of  $M_{RF1}$  and  $R_{CS1} ||R_{F1}|| R_{F2}$  because they are all connected to  $V_{CS1}$  and taken to have approximately the same voltage dc voltage across for easy calculation.

Gain at  $V_{CS2}$  from  $V_{CS1}$ :

$$\frac{V_{CS2}}{V_{CS1}} = \frac{-A_2}{1 - A_2} \times \frac{1}{1 + s\omega_{amp \ 4}} \tag{19}$$

$$\omega_{amp\,4} \approx \frac{(R_{CS2}||R_{F2})C_{o,CS2}}{1 - A_2}$$

(20)

Where  $R_{F2} = r_{dsRF2}$  of  $M_{RF2}$  and  $R_{CS2} || R_{F2}$  because both are connected to  $V_{CS2}$  and taken to have approximately the same voltage dc voltage across for easy calculation.

Although gain shown in (17) and (19) decreases as  $R_{F1}$  and  $R_{F2}$ decreases respectively, the bandwidth decreases instead of increasing due to the increase in parasitic  $C_{gd}$  and  $C_{gs}$  of these transistors which contribute to  $C_{o,CS}$ . Thus a compensation technique is used by adding the variable  $R_L$  as well. Since  $R_L$  is parallel to  $R_{CS3}$ , the gain of that stage is equivalent to  $-g_{mCS3}(R_{CS3}||r_{dsRL})$ .

Gain at  $V_{CS3}$  from  $V_{CS2}$ :

$$\frac{V_{CS3}}{V_{CS2}} = -A_3 \tag{21}$$

Where  $A_3 = g_{mCS3}(R_L||R_{CS3})$ ,  $R_L = r_{dsRL}$  of  $M_{RL}$ .

As shown in (21), when  $R_L$  decreases the gain also decreases. The bandwidth will increase, which compensates for the decrease in bandwidth caused by the decrease in  $R_{F1}$  and  $R_{F2}$ . This creates a nearly constant bandwidth no matter the variable gain of the AGC and ensures that it works properly.

Gain at  $V_{CS3}$  from  $V_{rgc}$  when accounting for only  $M_{F1}$ ,  $M_{F2}$  and  $M_{L}$ :

$$\frac{V_{CS3}}{V_{rgc}} = -\frac{A_1 A_2 A_3}{(1 - A_1)(1 - A_2)(1 + s\omega_{amp \ 3})(1 + s\omega_{amp \ 4})}$$

(22)

#### **Combined Gain of Proposed TIA Amplifier**

For calculated gains in (13) and (22), care needs to be taken to prevent duplication when calculating  $M_{fb1}$  and  $M_{F1}$ ,  $M_{F2}$  and  $M_L$  separately.

The combined gain of  $V_{CS3}$  from  $V_{rgc}$ :

$$Z_{amp} = -\frac{A_1 A_2 A_3 (1 + s \omega_{fb1})}{\{(1 + s \omega_{amp 1})(1 + s \omega_{amp 2})(1 + s \omega_{fb1}) - A_1 A_2 A_{fb1}\}\{(1 - A_1)(1 - A_2)(1 + s \omega_{amp 3})(1 + s \omega_{amp 4})\}}$$

(23)

Where  $C_{buffer}$  is the load capacitance of the next stage which is the buffer. The bandwidth of the Amplifier stage is taken to be the bandwidth of the third CS stage as it is the limiting stage.

## **Combined Gain of Entire Proposed TIA**

Gain at  $V_{CS3}$  from  $I_{in}$ :

$$Z_{TIA} = Z_{pre} \times Z_{amp} \tag{24}$$

The buffer stage after the gain stage is a source follower with resistive load that acts as a voltage buffer to match to 50  $\Omega$ .

#### **Results and Discussion**

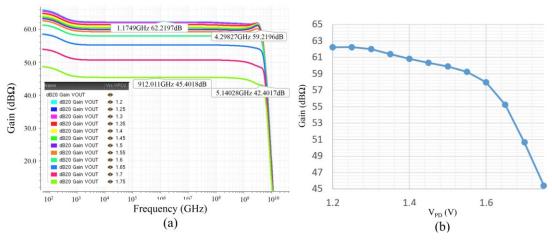

Figure 5. (a) Frequency response with varying V<sub>PD</sub> and (b) Gain variation versus V<sub>PD</sub>

Figure 5(a) shows the frequency response of the proposed TIA circuit. The maximum gain during the inactive mode of the AGC is measured at  $62.22~\mathrm{dB}\Omega$  and bandwidth is maintained above 4.3 GHz for  $C_{pd} = 0.25~\mathrm{pF}$  as  $V_{PD}$  increases with increasing input photodiode current. The usable frequency range is from 1 kHz to a constant 3dB bandwidth of above 4.3 GHz.

Figure 5(b) shows the Gain versus  $V_{PD}$  graph from the results in 5(a). As can be seen, from 1.2 V till 1.3 V, the AGC is inactive and the gain decreases minimally. Above 1.3 V, in the active mode, the AGC increasingly lowers the gain to a minimum of 45.4 dB $\Omega$  when it reaches 1.75 V. The maximum peaking of the graph occurs at  $V_{PD}$  = 1.5 V with a peak of 1 dB $\Omega$ . This shows that design is able to perform reliably as a variable gain AGC TIA.

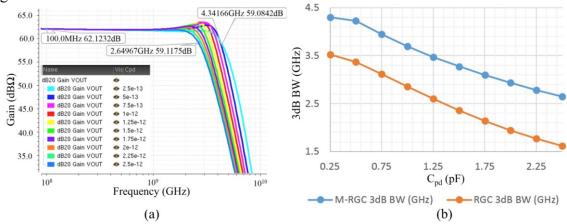

Figure 6. (a) Frequency Response with varying C<sub>pd</sub> and (b)BW variation versus C<sub>pd</sub>

In Figure6(a), when  $C_{pd}$  is increased from 0.25pF to 2.5pF (1000%), the gain remains constant and bandwidth decreases from 4.3 GHz to 2.65 GHz (drop 38.4%). The maximum peak of 1 dB $\Omega$  occurs at  $C_{pd}$  = 0.75pF. In Figure 6(b) not only is the bandwidth at  $C_{pd}$  = 0.25 pF higher (by 0.78 GHz), it alsodrops more slowly compared to the standard RGC input stage (with identical component parameters) with a gain of 61.35dB $\Omega$  (0.87dB $\Omega$  difference). Hence this demonstrates great resilience to input capacitance variation and input capacitance isolation of the bandwidth enhancing techniques.

A standard figure of merit (FOM) calculated as (25) is used to compare with other recent AGC TIA designs in Table 1 below.

$$FOM = \frac{Gain \ (\Omega) \times Bandwidt \ h \ (GHz) \times C_{pd} \ (pF) \times Gain \ Range \ (\max \ dB\Omega - \min \ dB\Omega)}{DC \ Power \ of \ core \ circuit \ (mW)}$$

(25)

|                           | [16] | [5]  | [17] | This Work |

|---------------------------|------|------|------|-----------|

| RF CMOS Technology (nm)   | 180  | 180  | 180  | 180       |

| Input Capacitance (pF)    | 0.25 | 0.9  | 0.25 | 0.25      |

| Maximum Gain (dBΩ)        | 53.8 | 66   | 69.3 | 62.22     |

| Maximum Gain (Ω)          | 490  | 1995 | 2917 | 1291      |

| Minimum Gain (dBΩ)        | 44.6 | 48   | 55.8 | 45.40     |

| Minimum Gain (Ω)          | 170  | 251  | 616  | 186.2     |

| Gain Range (max dBΩ - min | 9.19 | 18   | 13.5 | 16.82     |

| $dB\Omega$ )              |      |      |      |           |

| Bandwidth (GHz)           | 9.1  | 1.5  | 1    | 4.3       |

| Core dc power (mW)        | 30   | 27   | 6    | 7.72      |

| FOM                       | 341  | 1795 | 1641 | 3021      |

Table 1. Comparison of this work with previous works

As shown in Table 1 above, the proposed design has a better FOM compared with other recent papers. Firstly, the gain range of  $16.82~\text{dB}\Omega$  which is the second highest proves that the proposed variable  $R_{F1}$ ,  $R_{F2}$  and  $R_L$  design is effective. Secondly, bandwidth of 4.3 GHz is also the second highest which proves the proposed bandwidth enhancing techniques in the RGC input stage and AGC amplifier stage. Thirdly, the core dc power of 7.72 mW is also the second lowest.

There are several advantages of the proposed design. Firstly, as shown in Table 1, the proposed design provides reasonable gain and bandwidth for a low power consumption. Secondly, due to the isolation of the input capacitance  $C_{pd}$ , the design allows a large variation of  $C_{pd}$  without much bandwidth loss. Thirdly, the design utilizes an innovative gain variation technique while maintaining bandwidth. Lastly, the design is fully analog controlled without any analog-to-digital converter (ADC) and digital control components for the AGC. It also has no inductors. Thus these factors help to ensure a small chip size.

#### **Conclusion**

This paper showsan inductorless variable-gain RGC TIA design using GlobalFoundries 0.18-µm CMOS technology. Not only does it have new bandwidth enhancing techniques that protectsthe large input capacitive load from bandwidth determination, it also has a novel method of varying the gain by maintaining a high bandwidth.

## Acknowledgements

The authors would like to thank the Singapore University of Technology and Design (SUTD) for their support and Global Foundries for their process design kit (PDK).

#### References

[1] Lu, Z., et al. (2007). "Broad-Band Design Techniques for Transimpedance Amplifiers." IEEE Transactions on Circuits and Systems I: Regular Papers 54(3): 590-600.

- [2] Lu, Z., et al. (2009). An inductor-less broadband design technique for transimpedance amplifiers. Integrated Circuits, ISIC '09. Proceedings of the 2009 12th International Symposium on.

- [3] Sackinger, E. (2010). "The Transimpedance Limit." Circuits and Systems I: Regular Papers, IEEE Transactions on 57(8): 1848-1856.

- [4] Liu, L., et al. (2014). "A high gain wide dynamic range transimpedance amplifier for optical receivers." Journal of Semiconductors35(1): 015001.

- [5] Royo, G., et al. (2016). CMOS transimpedance amplifier with controllable gain for RF overlay. 2016 12th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME).

- [6] Momeni, O., et al. (2010). "A 10-Gb/s Inductorless Transimpedance Amplifier." IEEE Transactions on Circuits and Systems II: Express Briefs 57(12): 926-930.

- [7] Lu, Z., et al. (2010). "Design of a CMOS Broadband Transimpedance Amplifier With Active Feedback." IEEE Transactions on Very Large Scale Integration (VLSI) Systems 18(3): 461-472.

- [8] Sung Min, P. and Y. Hoi-Jun (2004). "1.25-Gb/s regulated cascode CMOS transimpedance amplifier for Gigabit Ethernet applications." Solid-State Circuits, IEEE Journal of 39(1): 112-121.

- [9] Aznar, F., et al. (2011). "A 0.18-µm CMOS transimpedance amplifier with 26 dB dynamic range at 2.5 Gb/s." Microelectronics Journal 42(10): 1136-1142.

- [10] Joyner, V. M. and Y. Zhang (2009). A CMOS Analog Front-end Receiver with Desensitization to Input Capacitance for Broadband Optical Wireless Communication.

- [11] B.S.S. Lee, Y.S. Tan, T.B. Kumar, K.S. Yeo, Z.C. Li, X.P. Yu (2016). An Inductorless Transimpedance Amplifier design for 10 Gb/s optical communication using 0.18-µm CMOS. 15th International Symposium on Integrated Circuits (ISIC).

- [12] Young-Ho, K. and L. Sang-Soo (2013). A  $72dB\Omega$  11.43mA novel CMOS regulated cascode TIA for 3.125Gb/s optical communications. SOC Conference (SOCC), 2013 IEEE 26th International.

- [13] Chong Whye, S., et al. (2013). A low power wideband differential transimpedance amplifier for optical receivers in 0.18-µm CMOS. New Circuits and Systems Conference (NEWCAS), 2013 IEEE 11th International.

- [14] Zhu Lei, Y. M. C., Ling Tian, Li Zhang (2012). "A 10Gb/s Low-Power Front-End Amplifier for Optical Receiver in 0.18µm CMOS Technology." Advanced Materials Research: 872-875.

- [15] Sangirov, J., et al. (2013). "10 Gbps Transimpedance Amplifier-Receiver for Optical Interconnects." Journal of the Optical Society of Korea 17(1): 44-49.

- [16] Jia, X. and L. Zhenghao (2011). A 10 GB/s CMOS transimpedance amplifier with adaptive gain. Electric Information and Control Engineering (ICEICE), 2011 International Conference on.

- [17] Chen, R. Y. and Z. Y. Yang (2016). "CMOS Transimpedance Amplifier for Gigabit-per-Second Optical Wireless Communications." IEEE Transactions on Circuits and Systems II: Express Briefs 63(5): 418-422.