# Electrical Performance Simulation of 2.5D Package

Wenchao Tian and Zhanghan Zhao\*

School of Electro-Mechanical Engineering Xidian University, Xi'an, 710071, China

\*Corresponding author

*Abstract*—In this paper, the influence of TSV geometry parameters on transmission performance is analyzed and some TSV design references are given according to the simulation results. In addition, including coplanar waveguide (CPW) and microstrip line (MSL), two main signal line structures of RDL layer are studied and their transmission performance is compared.

Keywords-through silicon via; electrical performance simulation; silicon interposer; 2.5D package

## I. INTRODUCTION

With the development of IC industry, the latency and power consumption issues associated with metal interconnection in traditional two-dimensional architectures severely constrain the further development of integrated ICs<sup>[1]</sup>. Three-dimensional integration using TSV (Through Silicon Via) is considered one of the most promising and viable next-generation large-scale chip solutions<sup>[2][4]</sup>, while its application is subject to defects in the process. The 2.5D package can be achieved from traditional packaging to 3D packaging transition: It is a number of chips placed side by side on the silicon interposer, and then through the micro-bumps and the RDL (Redistribution Layer) connected, and then TSV and Bumps, thereby realizing the electrical connection of the silicon interposer to the package substrate. As the basis of 2.5D package, the wiring board on the silicon interposer density will lead to increased high-speed signal line spacing, adjacent to the crosstalk is more prone to problems. In addition, bumps and other non-continuous structure will seriously affect the high-speed signal transmission quality<sup>[6] [7]</sup>. In this paper, the signal integrity of the 2.5D package is studied in detail based on the transmission characteristics of the TSV channel and the electrical properties of the RDL high-speed signal transmission structure.

## II. ANALYSIS OF TSV TRANSMISSION CHARACTERISTICS

# A. TSV Model Variable Settings

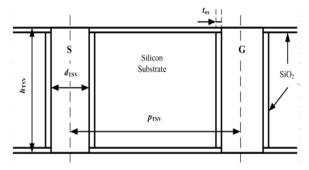

The ground-signal (G-S) TSV circuit model is established to analyze the effect of geometric parameters on the transmission characteristics of TSV.

FIGURE I. VARIABLE SETTINGS IN SIMULATION MODELS

TABLE I. GEOMETRIC VARIABLES AND PARAMETERS

| Geometric variables and parameters |          |                    |

|------------------------------------|----------|--------------------|

| Name                               | Value/µm | variation range/µm |

| r <sub>TSV</sub>                   | 9.5      | 8.5~10.5           |

| h <sub>TSV</sub>                   | 50       | 30~70              |

| <b>p</b> <sub>TSV</sub>            | 80       | 80~160             |

| tox                                | 1        | 0.2~1.8            |

# B. TSV Model Analysis Results

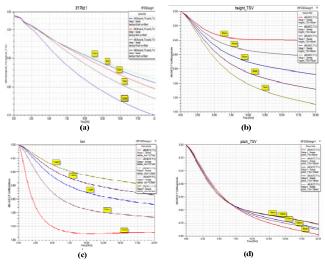

Influence of TSV radius on Transmission Performance

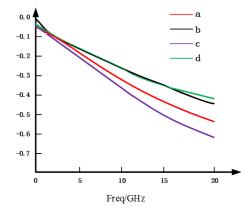

The parameter scan results for  $r_{TSV}$  are shown in the Figure 2(a): as the radius increases, the insertion loss gradually increases. At 10 GHz, the insertion loss at a radius of 8.5µm is 0.15 dB more than the radius of 10.5µm, means that the power loss to more than 20%.

FIGURE II. INFLUENCE OF GEOMETRIC PARAMETERS ON TSV INSERTION LOSSS

• Influence of TSV heights on Transmission Performance

The parameter scan results for  $h_{TSV}$  are shown in the Figure 2(b): TSV heights seriously affects the TSV transmission performance, insertion loss increases with the height of the TSV, the insertion loss at 70µm is about 0.8dB more than the insertion loss at 30µm, equivalent to 16% of the power loss.

• Influence of TSV heights on Transmission Performance

As shown in the Figure 2(c), the TSV signal transmission characteristics increase with the  $t_{ox}$ . The insertion loss at 70µm is about 0.8dB more than the insertion loss at 30µm, which is a very serious impact on signal and power integrity.

Influence of TSV pitchs on Transmission Performance

Parameter scan for  $p_{TSV}$ : As the TSV pitch increases, the insertion loss gradually decreases. The insertion loss at TSV pitch of 80 $\mu$ m is approximately 0.1 dB greater than the TSV pitch of 160 $\mu$ m, or 3% of the power loss. When the TSV pitch is 140 $\mu$ m, the insertion loss does not change with increasing TSV pitch.

C. TSV Design References

TLANTIS

PRESS

Through the TSV modeling and simulation and parameter analysis, combined with the manufacturing process, the following points are put forward for TSV design: TSV radius is smaller, more conducive to enhance the signal transmission performance, design TSV plating process should be allowed within the scope of selected small TSV radius. TSV height is smaller, the transmission performance is better. When the radius is the same, smaller height can achieve better aspect ratio and reduce the difficulty of electroplating. However, wafer thickness is too low will challenge the wafer polishing. Therefore, we must consider the transmission performance, the depth of the plating process and the follow-up process needs, select the appropriate TSV heights. The larger the TSV spacing is, the smaller the insertion loss is, but when the pitch is increased to a certain degree, the insertion loss is no longer reduced (the pitch value in this model is 140µm). In the TSV design, the spacing should be selected around the corresponding value, can take into account the signal transmission quality and interconnect density. Thicker TSV sidewall insulation layer is conducive to increase the insulation performance, reduce the leakage current coupled to the substrate to improve the signal transmission quality.

## III. STUDY ON ELECTRICAL PROPERTIES OF RDL SIGNAL TRANSMISSION STRUCTURE

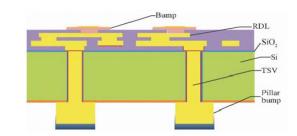

As the key structure of the vertical interconnection, the transmission characteristic of TSV is analyzed. This chapter examines the RDL that connects the microbumps to the TSV. The structure of the silicon interposer is shown in Figure 3

FIGURE III. 2.5D SILICON INTERPOSER STRUCTURE DIAGRAM

A. Research on RDL Single-ended Transmission Line of Silicon Interposer

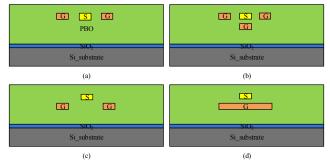

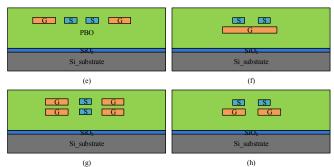

FIGURE IV. FOUR SINGLE-ENDED TRANSMISSION LINE STRUCTURES

In Figure 4, the wiring of group (a) is located in the RDL2 layer farther from the silicon substrate, the signal line and the ground line width are 10 $\mu$ m. Group (b) is on the basis of its additional 10 $\mu$ m wide ground line. Group (c) signal lines and ground lines are not in the same plane, line width of 10 $\mu$ m. Group (d) with a thicker ground to simulate the ground plane, the width of 60 $\mu$ m, can be equivalent to microstripline.

FIGURE V. INSERTION LOSS CURVES OF FOUR SINGLE - ENDED TRANSMISSION LINES

According to the  $S_{21}$  curve, the transmission performance of group (d) is optimal. However, the coarser ground wire limits its use in high-density interposer, and its thickness of the dielectric layer requirements can not match the current process, as long as the microstrip line parameters change, it is prone to impedance mismatch<sup>[3]</sup>. At 20GHz, the insertion loss of group (b) is greater than -0.5dB, which can meet the electrical performance requirements.

# B. Research on RDL Differential Transmission Line of Silicon Interposer

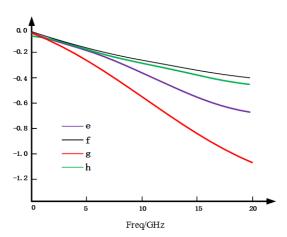

Figure 6 shows four differential pair routing schemes on the silicon interposer. The width of signal lines and ground lines are  $10\mu m$  and  $20\mu m$ , respectively. Group (f) is an analog microstrip line structure, a  $60\mu m$  ground wire is used to simulate the ground plane.

FIGURE VI. FOUR DIFFERENTIAL TRANSMISSION LINE STRUCTURES

FIGURE VII. INSERTION LOSS CURVES OF FOUR DIFFERENTIAL TRANSMISSION LINES

From the transmission parameter curve of Figure 7, the transmission performance of (f) microstrip line is the best, because a wider ground reduces the coupling to the substrate energy, thereby reducing the substrate loss. In group (g), the difference of the two signal lines from the silicon substrate leads to poor signal transmission quality. Two ground lines are added below the signal lines in group (h) and it can better meet the transmission performance requirements.

#### IV. CONCLUSION

In this paper, the TSV simulation model is established. The parameters of TSV radius, heights, oxide spacer thickness and pitchs are scanned. Then the influence of TSV on the transmission performance is analyzed according to the simulation results of insertion loss and the reference of TSV design is put forward. In addition, the layout of the highdensity signal transmission line of the RDL layer is studied. The transmission of the coplanar waveguide transmission line and the microstrip line are introduced and compared. For the single-ended transmission signal and differential transmission signal, specifically given the excellent transmission performance of the wiring.

#### ACKNOWLEDGMENT

Wenchao Tian thanks to National Natural Science Foundation: 61176130.

Wenchao Tian thanks to Ningbo Municipal Science Foundation License: 2016A610030.,

#### REFERENCES

- [1] Philip Garrou, 3-D ICs Enter Commercialization, Semiconductor International, 2008, 31, (12): 44-49.

- [2] Van der Plas G, Limaye P, Loi I, Mcrcha A, et al.Design Issues and Considerations for Low-Cost 3-D TSV IC Technology[J], IEEE Journal of Solid-State Circuits, 2011, 46(1): 293-307

- [3] M. Pozar. Microwave Engineering [M]. Publishing House Of Electronic Industry, 2006.

- [4] Vivek Singh. Lithography at 14nm and beyond: Choices and challengers[C].Design Automatio

- [5] M.Swaminathan. Power Integrity Modeling and Design for Semiconductors and System [M].Publishing House Of Electronic Industry, 2009.

- [6] J.Lauren. Through-Silicon Vias for 3D Integration [M].Chemical Industry Press,2014.

- [7] Sung T, Chiang K, Lee D, et al. Electrical analyses of TSV-RDL-bump of interposers for high-speed 3D IC integration[C]// Electronic Components and Technology Conference. IEEE, 2012:865-870.