6th International Conference on Energy, Environment and Sustainable Development (ICEESD 2017)

# The study of Forming process and Modeling of Bidirectional Self-Rectifying Pt/TiO<sub>2</sub>/Al Structured RRAM

Gang Liu<sup>1, a</sup>, Liang Fang<sup>2,b</sup>

**Keywords:** Resistive random access memory (RRAM), electroforming process, Pt/TiO<sub>2</sub>/Al, bidirectional self-rectifying.

**Abstract.** The forming process and SET-RESET mechanism of Pt/TiO<sub>2</sub>/Al resistive random access memory (RRAM) are investigated. Forming process was implemented by consecutive voltage sweep instead of one-step operation. After forming process, bidirectional self-rectifying characteristics was exhibited. In following SET and RESET operation with  $\pm 3V$  bias, this device can be used as a selector-less device without additional process steps. The characteristics of normal resistive switching is explained by analytical model and verified through simulation.

## Introduction

RRAM has received significant attention due to its high scalability, fast write/erase operation, low power consumption and relatively simple fabrication process compared with conventional Flash technology [1, 2]. Although the switching characteristics have been explained by many theories, the switching mechanisms are still not fully understood, the most problematic step is the electroforming process of these metal oxide resistive switching (RS) materials [3]. Typically this process is executed only one time for a memory array, and stable resistance switching could be realized after this step. In this paper, the dependence of Pt/TiO<sub>2</sub>/Al RS devices on electroforming is investigated. By perform measurement with various levels of sweep voltage and compliance current, the relation of pristine and electroformed devices were investigated. The bidirectional self-rectifying characteristics, which is helpful to suppress sneak current [4], and the SET/RESET switching mechanism are discussed. This whole procedure can be verified by simulations based on analytical model.

## **Experiments**

A 1.6  $\mu$ m thick positive photoresist (AZ5214) is spinning coated after a 1 $\mu$ m thick adhesive layer on the wafer with 200 $\mu$ m meter thick silicon dioxide for isolation layer, then an overhanging resist structure was developed. For adding adhesive of the bottom electrode (BE), 5nm Ti was fabricated, followed by BE metal Al. To form a 40nm thick resistive function layer, amorphous TiO<sub>2</sub> was chosen as the ionization source. Top electrode (TE) was fabricated using Pt, and the final structure of our array is Pt/TiO<sub>2</sub>/Al/Ti/SiO<sub>2</sub>/Si. Both metal and TiO<sub>2</sub> layer were fabricated by electron beam evaporation (EBE) technology and the width of BE and TE metal line is  $2\mu$ m. The selected device was addressed by connecting corresponding word line and bit line electrodes.

## **Characteristics of Electroforming process**

In many resistive devices, forming process is essential to RRAM cell, for it causes the creation of conductive path (filament) from pristine state and stabilizes SET and RESET operations [3].

<sup>&</sup>lt;sup>1</sup> School of Computer, National University of Defense Technology, Changsha, Hunan 410073, China

<sup>&</sup>lt;sup>2</sup> School of Computer, National University of Defense Technology, Changsha, Hunan 410073, China a38672251@qq.com, b Ifang\_cs@163.com

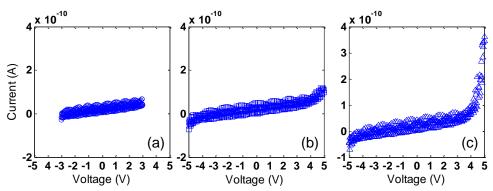

Fig. 1. DC sweep I-V curves of  $Pt(TE)/TiO_2/Al(BE)$  pristine device. (a) First sweep, voltage from -3V to +3V then repeat sweep in reverse; (b) Second and (c) Third sweep from -5V to +5V then repeats in reverse.

In forming process test, 3V, 5V and 6V voltage were used to detect the I-V characteristic of forming step. In all electrical characterization, bias voltage was applied on the BE, whereas the TE is grounded. Unless specified, all sweep direction were followed as: negative voltage $\rightarrow$ 0 $\rightarrow$ positive voltage $\rightarrow$ 0 $\rightarrow$ negative voltage. First,  $\pm$ 3V and  $\pm$ 4V sweep bias were applied to the cell as shown in Fig. 1. There is no noticeable change of cell conductance which indicates that neither  $\pm$ 3V nor  $\pm$ 4V can provide sufficient electrical field to build a conductive path in pristine device.

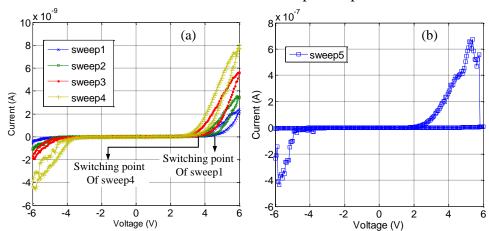

Fig. 2.Five successive dc sweep I-V curves of Pt(TE)/TiO<sub>2</sub>/Al(BE) pristine device in forming step, bias voltage from -6V to 6V.

To enhance forming effect, sweep bias voltage were set to  $\pm 6V$ . As shown in Fig. 2(a). Sweep1-4 are 4 successive repetitive sweep cycles, in each sweep cycle, cell current in positive sweep (bias voltage from -6V to 6V) is different from negative sweep (bias voltage from 6V to -6V) at the same bias voltage. It indicates that 6v voltage is enough to process forming step, and the switching point (bias voltage that make the current begin to rise apparently) decreases with cycling number increases. After 4 cycles using  $\pm 6V$  sweep, cell current increases rapidly in sweep5 as shown in Fig. 2(b). Because the filament which created by forming voltage has a large conductivity, it grows under bias voltage, when this filament connects the TE and BE by initialize a conducting path, device current increases rapidly. So it's reasonable to believe that the device after sweep5 in Fig. 2(b) is close to a critical point that the filament is completely formed in LRS. The creation process of metallic filament in TiO<sub>2</sub> was regarded as the transformation that from TiO<sub>2</sub> to Ti<sub>n</sub>O<sub>2n-1</sub> (mostly n=4 or 5) [5], measurement data above indicates that this transformation cannot be realized in a single step, so multiple forming cycles is necessary.

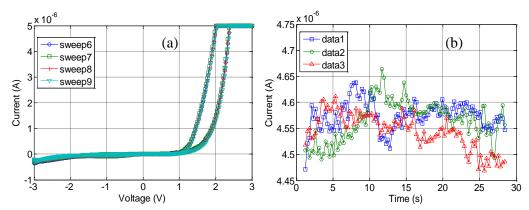

After forming step, bias voltage from 3V to -3V was applied to device again. As shown in Fig. 3(a), 4 successive sweeps were performed, that indicates that the device can be configured to HRS by -3V and LRS by 3V, compliance current was set to  $5\mu$ A.

Fig. 3.I-V characteristics of 5 successive sweeps after forming step, I-t of Pt(TE)/TiO<sub>2</sub>/Al(BE) device with 2V bias voltage on Al electrode for about 30s.

After SET operation, 2V bias voltage was applied to device for 30 seconds to confirm that after forming step, filament that connects TE and BE can be set to a stable state by 3V.

#### **Analysis and Modeling**

Many researches have proposed that oxygen vacancies  $(V_0^{2+})$  as one of the main point defects in transition metal oxide plays an important role in electrical conduction property [5, 6]. According to Fig. 3, it is speculated that, conductive path can be repaired by SET voltage (3V in this paper) after forming step.  $V_0^{2+}$  can be regarded as mobile +2-charged dopants [7], when positive voltage was applied to the Al electrode, electrical field drive  $V_0^{2+}$  towards cathode. For the metal/semiconductor contact can be transformed into Ohmic in the case of very heavy doping [8], the resistivity of Pt/TiO<sub>2</sub> interface is thus reduced.

There is a bidirectional rectifying character in LRS when bias voltage between -3V and  $\sim$ 1.2V as shown in Fig. 3(a), this is different from traditional bipolar RRAM characteristic. The rectifying character may due to the forming of AlO<sub>x</sub> barrier which created by the oxidation at Al/TiO<sub>2</sub> interface [9].

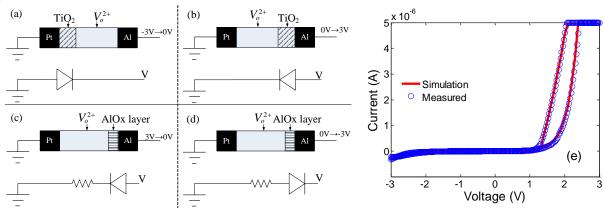

Fig. 4. Analytical model under various voltage bias conditions. Schottky barrier is depicted as diode, filament is depicted as resistor. (a) HRS, negative bias applied on BE. (b) HRS, positive bias applied on BE. (c) LRS, positive bias applied on BE. (d) LRS, negative bias applied on BE. (e) I-V curves of  $Pt(TE)/TiO_2/Al(BE)$  simulation and measured data.

To understand the appearance of both positive and negative polarities of bias voltage in the Pt(TE)/TiO<sub>2</sub>/Al(BE) device, an analytical model was created based on the following assumptions:

1) Conduction mechanism in HRS is dominated by TiO<sub>2</sub>/Metal Schottky-like barrier which is depicted by diode in Fig. 4(a) and Fig. 4(b). Conduction is modeled using typical Schottky Current-Voltage equation [8]

$$J = \left[ A^* \cdot T^2 \cdot exp\left(\frac{-e\phi_B}{kT}\right) \right] \left[ exp\left(\frac{eV_a}{kT}\right) - 1 \right]$$

(1)

Where  $A^*$  is the effective Richardson constant, T the absolute temperature,  $\phi_B$  the barrier height, and  $V_a$  the forward bias voltage.

2) The I-V Characteristic of the LRS is depicted by resistor-diode series connection model, as shown in Fig. 4(c) and Fig. 4(d). The behavior of AlO<sub>x</sub> is depicted by diode also using (1). Hopping conduction mechanism is chosen to model filament conduction which is depicted by resistor [10].

$$J = 2e \cdot RkT \cdot N(E_F) \nu_{ph} \exp\left(-2\alpha R - \frac{W}{kT}\right) \sinh\left(\frac{eRF}{kT}\right)$$

(2)

Where  $N(E_F)$  is the density of state, R is electron jumping distance,  $v_{ph}$  depends on the phonon frequencies, W is the difference between the energies of the two states. The simulation curve of the model as expressed with Eq. 1 and Eq. 2 are shown in Fig. 4(e). Simulation curve is in good agreement with measured data as shown in Fig. 4(e).

#### **Conclusions**

The forming process and SET/RESET operation of Pt(TE)/TiO<sub>2</sub>/Al(BE) RRAM have been investigated in this paper. Forming process needs a higher voltage to start up and multi-cycles to complete in this device. In stable SET/RESET operation, the resistive switching characteristic is explained properly through an analytical model. Simulation results from the model proposed helps to understand the mechanism of the device and would assist further circuit design.

## References

- [1] Lien, C. H., et al. "The highly scalable and reliable hafnium oxide ReRAM and its future challenges." Proc. IEEE ICSICT (2010): 1084-1087.

- [2] Chen Y S, Lee H Y, et al. Challenges and opportunities for HfO<sub>x</sub> based resistive random access memory, (IEDM), 2011 IEEE International. IEEE, 2011: 31.3. 1-31.3. 4.

- [3] Kalantarian, A., et al. Controlling uniformity of RRAM characteristics through the forming process. in Reliability Physics Symposium (IRPS), 2012 IEEE International. 2012. IEEE.

- [4] J. Woo et al., "Multi-layer tunnel barrier (Ta<sub>2</sub>O<sub>5</sub>/TaO<sub>x</sub> /TiO<sub>2</sub>) engineering for bipolar RRAM selector applications," in Proc. Symp. VLSI Technol., Jun. 2013, pp. T168–T169.

- [5] D.-H. Kwon, K. M. Kim, J. H. Jang, J. M. Jeon, M. H. Lee, G. H. Kim, X.-S. Li, G.-S. Park, B. Lee, S. Han, M. Kim, and C. S. Hwang, "Atomic structure of conducting nanofilaments in TiO2 resistive switching memory", Nat. Nanotechnol., vol. 5, no. 2, pp. 148 153, Feb. 2010.

- [6] D. Lee et al., "Defect engineering using bilayer structure in filament-type RRAM," IEEE Electron Device Lett., vol. 34, no. 10, pp. 1250–1252, Oct. 2013.

- [7] D. Strukov, G. Snider, D. Stewart, and R. Williams, "The missing memristor found," Nature, vol. 453, no. 7191, pp. 80–83, May 2008.

- [8] Neamen D A, Pevzner B. Semiconductor Physics and Devices: basic principles [M]. New York: McGraw-Hill, 2003

- [9] Minseok Jo, Dong-jun Seong, et al, "Novel Cross-point Resistive Switching Memory with Self-formed Schottky Barrier", 2010 Symposium on VLSI Technology.

- [10] Wei Z, Takagi T, Kanzawa Y, et al. Demonstration of high-density ReRAM ensuring 10-year retention at 85 C based on a newly developed reliability model, (IEDM), IEEE, 2011: 31.4. 1-31.4. 4.